# FELIX User Manual

ATLAS FELIX Group

<<<

# **Table of Contents**

| 1. Welcome to the FELIX User Manual                     | 1  |

|---------------------------------------------------------|----|

| 1.1. Overview                                           | 1  |

| 1.2. Document Compatibility                             | 1  |

| 2. Introduction to FELIX                                | 3  |

| 2.1. FELIX Variants and Functionality                   | 3  |

| 2.1.1. Gigabit Transceiver (GBT) and the Versatile Link | 3  |

| 2.1.2. FULL Mode                                        | 3  |

| 2.1.3. Propagation of ATLAS TTC Information             | 4  |

| 3. Hardware Requirements and Setup                      | 5  |

| 3.1. Recommended Hardware Platforms                     | 5  |

| 3.1.1. FPGA I/O Hardware: VC-709 (Commodity Platform)   | 5  |

| 3.1.2. FPGA I/O Hardware: Custom Platforms              | 5  |

| 3.1.3. FELIX Host Systems                               | 7  |

| 3.2. Installation of VC-709                             | 7  |

| 3.3. Installation of BNL-711 and BNL-712                | 7  |

| 3.4. Connecting to an existing TTC system               | 8  |

| 3.4.1. VC-709 Only: TTCfx v3 Overview and Installation  | 8  |

| 3.4.2. Connecting TTC and BUSY                          | 9  |

| 3.5. Configuring FELIX Clock                            | 9  |

| 3.5.1. Clock Source Selection                           | 9  |

| 3.5.2. TTC Clock Recovery: ADN2814                      | 10 |

| 3.5.3. Clock Jitter Cleaning                            | 10 |

| 3.6. Connecting and Initialising Optical Links.         | 11 |

| 3.6.1. Physical Link Layer Status: VC-709               | 11 |

| 3.6.2. Physical Link Layer Status: BNL-711/712          | 11 |

| 3.6.3. Logical Link Layer Initialisation                | 12 |

| 4. Firmware Releases and Programming                    | 13 |

| 4.1. Firmware Distribution Protocol                     | 13 |

| 4.1.1. Release Announcements                            | 13 |

| 4.1.2. Firmware Distribution Site                       | 13 |

| 4.1.3. Supported Link Protocols & Encoding              | 13 |

| 4.2. Firmware Programming                               | 13 |

| 4.2.1. JTAG Connectivity                                | 14 |

| 4.2.2. Setting up the Vivado™ Suite                     | 14 |

| 4.2.3. Programming the FPGA Directly                    | 17 |

| 4.2.4. Programming the FLASH ROM (VC-709)               | 19 |

| 4.2.5. Programming the FLASH ROM (BNL-711/712)          |    |

| 4.2.6. Enabling new FPGA Configuration                  | 22 |

| 5. Software Distribution and Installation                       | 24 |

|-----------------------------------------------------------------|----|

| 5.1. Software Distribution Protocol                             | 24 |

| 5.1.1. Pre-requisites                                           | 24 |

| 5.1.2. Release Announcements                                    | 24 |

| 5.1.3. Release Distribution Site                                | 24 |

| 5.2. Software Installation Instructions                         | 24 |

| 5.2.1. Driver RPM Installation Instructions                     | 24 |

| 5.2.2. Installation of FELIX Software Suite                     | 26 |

| 6. Basic Tools                                                  | 28 |

| 6.1. E-link Configuration with elinkconfig                      | 29 |

| 6.1.1. Global Panel                                             | 31 |

| 6.1.2. To-Host Panel                                            | 34 |

| 6.1.3. From-Host Panel                                          | 35 |

| 6.1.4. Link and Data Generator Configuration Upload Dialog      | 36 |

| 6.1.5. Guide to Valid E-link Configurations                     |    |

| 6.1.6. Guide to common configuration tasks                      | 39 |

| 6.2. Low Level Tools (System Status Monitoring & Control)       | 41 |

| 6.2.1. flx-info                                                 | 42 |

| 6.2.2. flx-config                                               | 43 |

| 6.2.3. flx-init                                                 | 44 |

| 6.2.4. flx-reset                                                | 45 |

| 6.2.5. flx-monitor                                              | 46 |

| 6.3. Dataflow from Front-end via FELIX to FELIX host PC         | 47 |

| 6.3.1. fdaq                                                     | 47 |

| 6.4. Dataflow from FELIX Host PC to Front-end Systems via FELIX | 49 |

| 6.4.1. fupload.                                                 | 49 |

| 6.5. FELIX Configuration Tools                                  | 51 |

| 6.5.1. felink                                                   | 51 |

| 6.5.2. fereverse                                                | 52 |

| 6.5.3. fgpolarity.                                              | 53 |

| 6.5.4. feconf                                                   | 54 |

| 6.5.5. femu                                                     | 55 |

| 6.5.6. feto                                                     | 55 |

| 6.5.7. fflash                                                   | 56 |

| 6.6. General Debugging Tools                                    | 57 |

| 6.6.1. fcheck.                                                  | 57 |

| 6.6.2. fedump                                                   | 58 |

| 6.6.3. fec                                                      | 59 |

| 6.7. Remote Hardware Command and Configuration Tools            | 60 |

| 6.7.1. fic(e)                                                   | 60 |

| 6.7.2. fgbtxconf                                                | 61 |

| 7. Felixcore Application and NetIO                                  | 63 |

|---------------------------------------------------------------------|----|

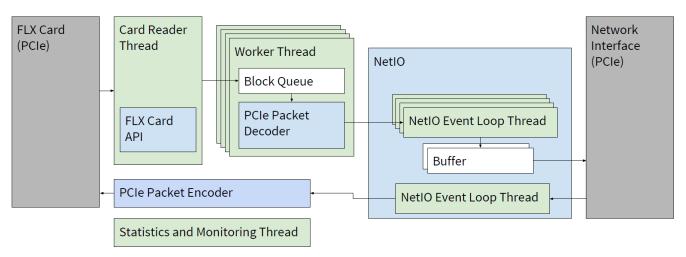

| 7.1. Operational Principles                                         | 63 |

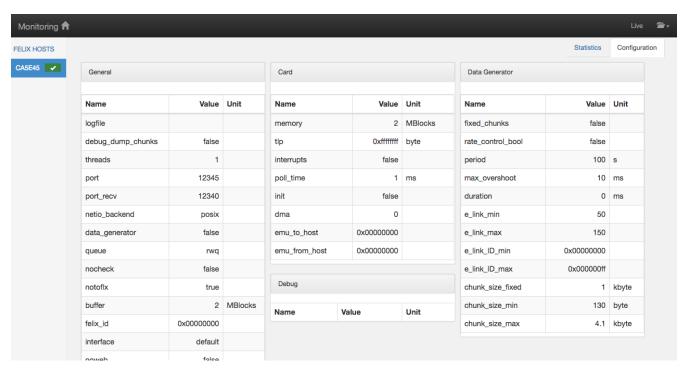

| 7.2. Configuration                                                  | 63 |

| 7.3. Monitoring                                                     | 65 |

| 7.3.1. FelixCore Native Monitoring                                  | 65 |

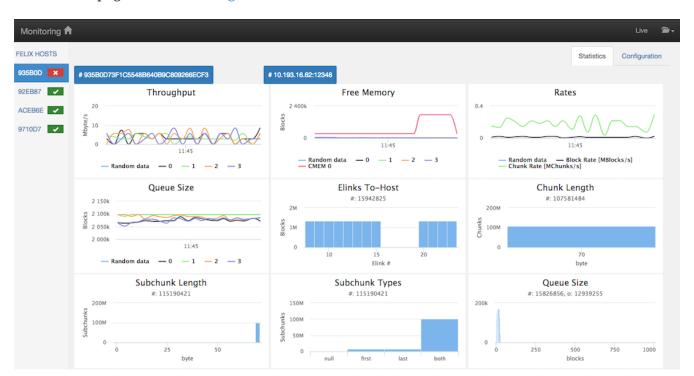

| 7.3.2. Monitoring with felix-web-mon                                | 65 |

| 7.4. FelixCore Examples                                             | 68 |

| 7.4.1. Tests without an FLX Card                                    | 68 |

| 7.4.2. Tests with an FLX Card                                       | 68 |

| 7.5. Connecting to a felixcore instance using NetIO tools.          | 68 |

| 7.6. Connecting to a felixcore instance using FATCAT                | 69 |

| 7.7. Discovering E-links with the FELIX BUS system                  | 69 |

| 7.8. Debugging.                                                     | 70 |

| 7.8.1. Using the FelixCore event tracing framework                  | 70 |

| 8. Resources for Front-End Developers                               | 72 |

| 8.1. FELIX Firmware Modules for Front-end Users                     | 72 |

| 8.1.1. Downloading Firmware Source                                  | 72 |

| 8.1.2. GBT Test Modules                                             | 72 |

| 8.1.3. FULL Mode Test Modules                                       | 73 |

| 8.2. General Hints and Tips                                         | 73 |

| 8.2.1. Known Issues with GBTx.                                      |    |

| 8.2.2. Known Technical Requirements for FELIX Communication         | 73 |

| 8.2.3. Examples of Design Best Practice based on Current Experience | 73 |

| 8.2.4. Frequently Asked Questions                                   | 74 |

| Appendix A: Setting up a TTC System for use with FELIX              | 76 |

| A.1. Tuning a TTC system                                            | 78 |

| A.2. Guide to TTC Channel B                                         | 81 |

| A.2.1. B channel decoding firmware                                  | 83 |

| A.2.2. Channel B decoding software                                  | 83 |

| A.3. Useful documents                                               | 83 |

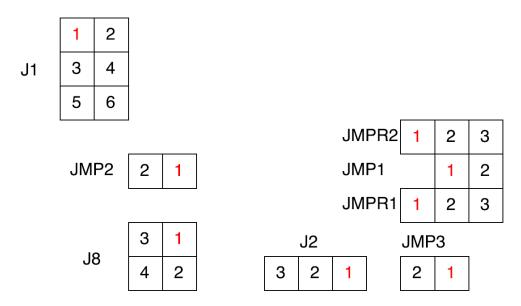

| Appendix B: BNL-711 Technical Information                           | 84 |

| B.1. User Jumper Map and Functional Specification                   | 84 |

| B.1.1. J1                                                           | 84 |

| B.1.2. J2                                                           |    |

| B.1.3. J8                                                           | 85 |

| B.1.4. JMP1                                                         |    |

| B.1.5. JMP2                                                         | 85 |

| B.1.6. JMP3                                                         | 86 |

| B.1.7. JMPR1 & JMPR2                                                | 86 |

| B.2. MiniPOD Connectivity Map                                       |    |

| Appendix C: Guide to FELIX Data Structures                          |    |

| Appendix D: Guide to Using FELIX with GBT-SCA                                           | 90 |

|-----------------------------------------------------------------------------------------|----|

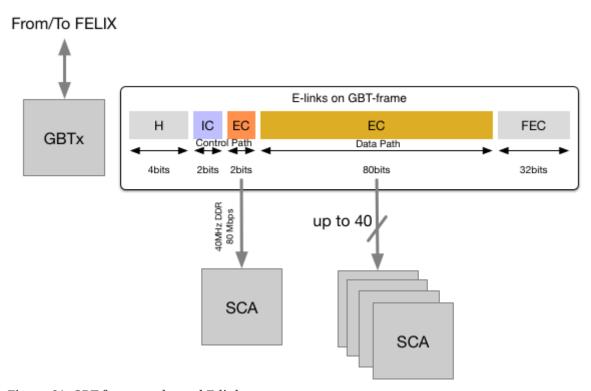

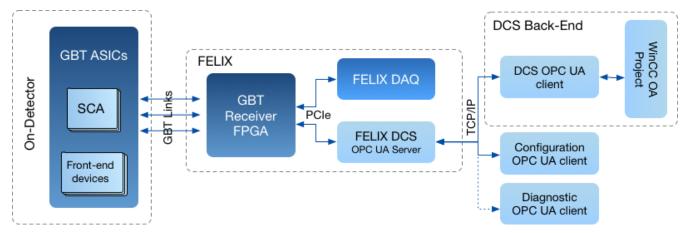

| D.1. Introduction                                                                       | 90 |

| D.2. Typical test setup                                                                 | 90 |

| D.3. Operation to set up an SCA e-link                                                  | 91 |

| D.4. Low level operations with fec tools to configure and establish basic communication | 93 |

| D.5. The integrated production system — Introduction                                    | 93 |

| D.6. The SCA software (SCA-SW), its demonstrators and the OPC-UA SCA Server             | 94 |

| D.6.1. SCA-SW library                                                                   | 94 |

| D.6.2. SCA OPC-UA server                                                                | 96 |

| D.7. SCA References                                                                     | 98 |

| References                                                                              | 99 |

# Chapter 1. Welcome to the FELIX User Manual

# 1.1. Overview

This document is intended to support all users of the Phase-I FELIX readout infrastructure with installation, maintenance and operation of their system. The document covers all aspects of the FELIX system from recommended hardware to firmware and driver installation and maintenance. Finally the full suite of FELIX software will be presented, including useful test tools leading up to the primary 'FelixCore' dataflow application which is intended to form the backbone of all data taking sessions. For more information users should consult the following locations for updates:

The FELIX users mailing list:

atlas-tdaq-felix-users@cern.ch

The FELIX Project Website:

https://atlas-project-felix.web.cern.ch/atlas-project-felix

The FELIX release distribution site:

https://atlas-project-felix.web.cern.ch/atlas-project-felix/user/dist/

User support requests from users to the FELIX team should be made via the dedicated JIRA project:

https://its.cern.ch/jira/projects/FLXUSERS

User support via SharePoint has been discontinued. Please report any broken links of obsolete material to help improve the overall quality of our documentation.

# 1.2. Document Compatibility

This document is continuously evolving alongside FELIX firmware and software. The table below will keep track of the versions of each which should be considered covered by a given version of this manual. Note - as of Register Map 4 the version number format for this document was changed to better align with other version numbers in the FELIX release. As such, the last version which is compatible with RM3 is 0.8x (i.e. in the old numbering).

| Manual Version | GBT F/W Revision | FULL Mode F/W<br>Revision | LTDB Mode F/W<br>Revision | Software Release |

|----------------|------------------|---------------------------|---------------------------|------------------|

| 4.0.5+         | rm-4.4.1         | rm-4.4.1                  | rm-4.4.1                  | 4.0.5            |

| 0.8x           | 5317+            | 5327/5168                 | N/A                       | 3.9.1            |

| 0.7            | 5317+            | 5327/5168                 | N/A                       | 3.8.1            |

| 0.61           | 5317             | 5327                      | N/A                       | 3.8              |

| Manual Version | GBT F/W Revision | FULL Mode F/W<br>Revision | LTDB Mode F/W<br>Revision | Software Release |

|----------------|------------------|---------------------------|---------------------------|------------------|

| 0.6            | 5214             | N/A                       | N/A                       | 3.7              |

| < 0.6          | 4400, 4500       | N/A                       | N/A                       | 3.4.2            |

# Chapter 2. Introduction to FELIX

FELIX is a new detector readout component being developed as part of the ATLAS upgrade effort. FELIX is designed to act as a data router, receiving packets from detector front-end electronics and send it to programmable peers on a commodity high bandwidth network. Whereas previous detector readout implementations relied on diverse custom hardware platforms, the idea behind FELIX is to unify all readout across one well supported and flexible platform. Rather than the previous hardware implementations, detector data processing will instead be implemented in software hosted by commodity server systems subscribed to FELIX data. From a network perspective FELIX is designed to be flexible enough to support multiple technologies, including Ethernet and Infiniband.

Given the general purpose nature of the FELIX effort, the system has also been adopted by several non-ATLAS projects. This document is therefore targetted at users both within and outside of the ATLAS upgrade effort.

# 2.1. FELIX Variants and Functionality

FELIX supports two different link protocols for the transfer of data to and from front-end peers. Each is supported by the same hardware platform, with separate firmware revisions both based on the same core modules.

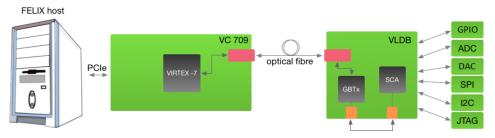

# 2.1.1. Gigabit Transceiver (GBT) and the Versatile Link

The Gigabit Transceiver (GBT) chipset and associated technologies were developed as part of CERN's Radiation Hard Optical Link Project[gbtmainpage]. The goal was to develop a radiation hard bi-directional link for use in LHC upgrade projects. GBT provides an interface an optical connectivity technology known as the Versatile link[versatilelink], which provides high bandwidth and radiation hard transport of data between GBT end points.

The GBT transmission protocol is designed to aggregate multiple lower bandwidth links from frontend electronics components into one radiation hard high bandwidth data link (running at up to 5 Gb/s). The logical lower bandwidth links which make up a GBT link are known as E-links. The details of how E-links are supported within the FELIX project are discussed in Section 6.1.5 of this document.

The GBT protocol has been implemented both in dedicated hardware (e.g. the GBTx chip[GBTx]) as well as directly on FPGA platforms, the latter of which has been built on for use by the FELIX project[GBTmanual].

#### **2.1.2. FULL Mode**

Within the context of the ATLAS upgrade (and subsequently externally) a requirement arose for a higher bandwidth data link from detector to FELIX than was possible with GBT, which has to support radiation hardness. These newer clients did not require radiation hardness, and were able to support a protocol which could be implemented in FPGAs on both sides of the link. The resulting development is known as 'FULL mode'[fullmodespec], referring to full bandwidth.

The FULL mode protocol is a implemented as a single wide data stream with no handshaking or logical substructure (i.e. no E-links). The reduced constraints mean that FULL mode links can operate at a line transmission rate of 9.6 Gb/s, which accounting for 8b10b encoding means a maximum user payload of 7.68 Gb/s.

Note that FULL mode in FELIX is currently only implemented in the from detector to FELIX direction, as there are currently no requirements for the to detector direction. FELIX FULL mode variants therefore implement to detector links with the GBT protocol, as this is sufficient for the required payloads.

## 2.1.3. Propagation of ATLAS TTC Information

As well as transferring data to and from front-ends, FELIX is also required to interface with the ATLAS Timing, Trigger and Control (TTC) system. FELIX must provide TTC information both to the front-ends at full granularity, and to network peers in a reduced form. The propagation of TTC information to the front-end is performed via dedicated E-links.

# Chapter 3. Hardware Requirements and Setup

# 3.1. Recommended Hardware Platforms

## 3.1.1. FPGA I/O Hardware: VC-709 (Commodity Platform)

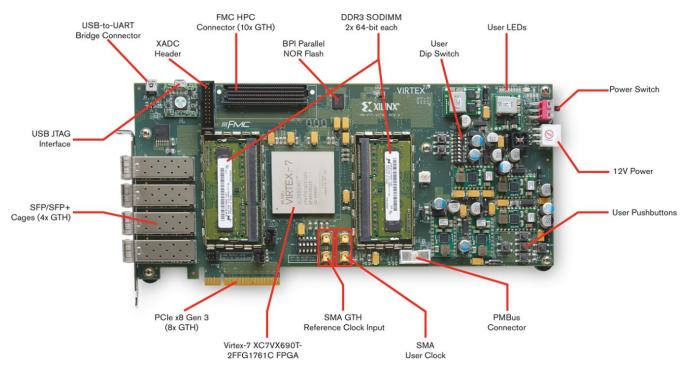

The hardware platform recommended for FELIX operation in detector test stands is based on the Xilinx® VC-709 Connectivity Kit[xilinxvc709]. This platform provides 4 optical transceivers compatible with both GBT and 'full mode' operation as well as a Xilinx® Virtex®-7 series FPGA and 8-lane PCIe Gen 3.0 interface. The TTC interface for the system is provided by the TTCfx v3 FMC mezzanine card. An image of the VC-709 board and guide to features is presented below.

Figure 1. The VC-709 development board.

#### 3.1.2. FPGA I/O Hardware: Custom Platforms

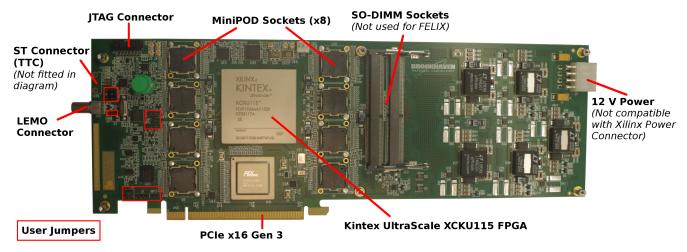

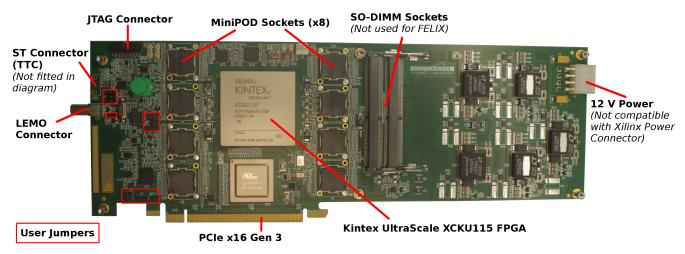

The hardware platform chosen for the final FELIX implementation in Phase-I is a custom interface board designed by BNL. The initial version used for FELIX is known as the BNL-711, with a modified design (BNL-712) selected for the final system.

#### **BNL-711**

The BNL-711 hosts a Xilinx® Kintex® UltraScale FPGA on a board capable of supporting 48 high speed optical links via MiniPOD transceivers, with a 16-lane PCIe Gen 3.0 interface. On-board clock jitter cleaning and TTC circuitry mean that no mezzanine attachment is required to connect with ATLAS clock and control systems. An image of the BNL-711 and its key features are presented below. While the board is still in use in a number of test stands, it is recommended that subdetector teams adopt the BNL-712 for any new developments.

Figure 2. The BNL-711 V1.5 board.

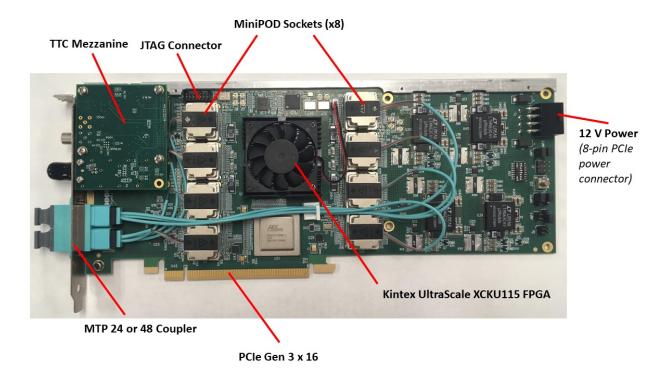

#### **BNL-712**

The BNL-712 (a.k.a. BNL-711 v2) is similar to the BNL-711 in that it hosts a Xilinx® Kintex® UltraScale FPGA on a board capable of supporting 48 high speed optical links via MiniPOD transceivers, with a 16-lane PCIe Gen 3.0 interface. The BNL-712 is a smaller card, saving space by not hosting the unused SO-DIMM slotsOn-board clock jitter cleaning on-board the BNL-712. Various other improvements to the FPGA pin-out to make it easier to route signals to both PCIe endpoints. In order to make the board compatible with future developments, the TTC circuitry has been moved to a mezzanine. This makes it possible to connect both to current ATLAS clock and control systems and candidates for future implementations. An image of the BNL-712 and its key features are presented below. BNL-712 cards are available for subdetector test stands for commissioning and integration. Please contact the FELIX group for more information.

Figure 3. The BNL-712 board.

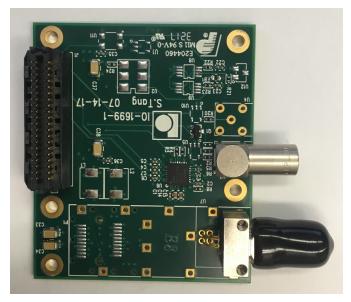

The timing mezzanine for the BNL-712 which is compatible with the ATLAS TTC System in Phase-I is show in Figure 4.

Figure 4. The ATLAS Phase-I TTC Mezzanine for the BNL-712.

For more detailed information on the BNL-712, please consult the dedicated user manual[flx-712].

## 3.1.3. FELIX Host Systems

The current recommended hardware platform for a VC-709 FELIX system is based on the Supermicro® X10SRA-F motherboard[X10SRA-F]. The system should be populated with at least 32 GB of DDR4 RAM and an Intel® Xeon $^{\text{TM}}$  E5 family CPU (v3 or v4) with at least six real cores. Please see the motherboard manufacturer specification for more details.

# 3.2. Installation of VC-709

For full details regarding the VC-709 please consult the manual provided with your equipment. In terms of installing the card into a FELIX system please follow the following guidelines. The VC-709 should be installed into an 8-lane or 16-lane Gen 3 PCIe slot on the host motherboard, taking into account the need for clearance on all sides. The board must be connected to power from the system's internal ATA power supply via a custom Molex adapter provided with the board. The power socket on the board is shown on the upper right hand corner of Figure 1, labelled '12V Power'. Ensure that the power switch, just above the socket, is switched to the on position.

The FPGA aboard the VC-709 is configured via an on-board JTAG programmer, which can be connected to a mini-USB cable with the 'USB JTAG Interface' on the top left of Figure 1. A right angled mini-USB connector is recommended to minimise obstruction of the hosts case lid, although a straight cable is provided for free with your kit. Note that this has currently only been tested for USB2, which is the recommended interface. In order to be able to program the card please connect it to a convenient USB port on your host machine, or to another machine which you wish to use as a programming server. Finally, ensure that the link transceivers are safely inserted into the on-board cages.

# 3.3. Installation of BNL-711 and BNL-712

The BNL-711/712 should be installed in a 16-lane Gen 3 PCIe slot on the host motherboard. The board must be connected to power from the system's internal ATA power supply via an 8-pin PCIe

power connector (of the type commonly used for graphics cards). Note that the board does not support use of Xilinx power connectors.

The BNL-711/712 provides a JTAG connector to which programmers can be connected for FPGA configuration. The Digilent® HS2 programmer is recommended for this purpose. Aboard the BNL-711/712 are a series of jumpers to permit users to reconfigure various I/O properties of the board. For a full specification of these please consult [app:bnl711] for the BNL-711 and the dedicated user manual for the BNL-712[xilinxvc709].

# 3.4. Connecting to an existing TTC system

This section is only relevant to users who wish to connect their FELIX system to a ATLAS TTC infrastructure. Other users should skip this section and proceed directly to clock configuration.

### 3.4.1. VC-709 Only: TTCfx v3 Overview and Installation

For VC-709 systems the TTCfx mezzanine card[CERN\_TTC\_FMC] is designed to connect your FELIX card to the ATLAS TTC system as used throughout Run 1-3 operations[ttc]. BNL-711/712 systems do not require this component as the same logic is implemented on the BNL-711/712 itself. The TTCfx is a small FMC mezzanine card, as shown in Figure 5, which can be attached to the VC-709 via the single FMC slot on-board (top left of Figure 1).

Figure 5. Image of a TTCfx v3 card.

To complete the installation, you must then connect the P and N SMA GTH Reference Clock inputs on the VC-709 (middle bottom of Figure 1) to the SMA connectors on the TTCfx v3 (P to P and N to N) via suitable SMA cables, [1: An example SMA cable is: http://eu.mouser.com/ProductDetail/Amphenol-RF/135103-01-0600/?qs=sGAEpiMZZMufBZYvsU/be\%2bYZgfjb/mihYZ4wKp9N4jE=]. The right angle side goes on the VC-709, to make the cable bending a bit more gentle. If you have space in your chassis, straight SMAs on both ends will do the job as well.

The TTCfx mezzanine card requires no specific firmware programming, and should work out of the box once connected to a TTC peer and a software configuration script is run. More detail is provided in the next section.

### 3.4.2. Connecting TTC and BUSY

This section assumes you are connecting a TTCvx-based system to FELIX. Notes on setting up such a system are available in [app:TTC]. Once set up, connect a TTC output from the TTCvx to the TTCfx v3 using a Multi-Mode fibre with ST connectors. The connector on the TTCfx v3 end is visible in Figure 5, on the upper left hand side. On the BNL-711 the ST and LEMO connectors are located on the upper left part of the board, as shown in Figure 2. On the BNL-712 they are integrated into the TTC mezzanine, as shown in Figure 3.

Finally, use a LEMO connector to connect the TTCfx v3 or BNL-711/712 to a destination for BUSY signals (as per your use case). The connector on the TTCfx v3 is visible in Figure 5 on the upper right hand side. The BUSY signal is the ATLAS standard open-collector BUSY signal, but with a weak 24 kOhm pull-up to 1.8 V to allow viewing on an oscilloscope.

# 3.5. Configuring FELIX Clock

This section assumes you have set up the FELIX software infrastructure as in Section 5. If you have not, then please do so before proceeding.

#### 3.5.1. Clock Source Selection

FELIX requires a clock source in order to synchronise propagation of signals both within the FPGA and to external peers. The FELIX firmware supports the use of both a received clock from an external TTC source as well as an internally generated clock for users who don't need or have access to a such a system.

Older firmware revisions did not support this feature, so please ensure your version is labelled with CLKSELECT to ensure compatibility.

To check your current clock selection, run the following command:

```

flx-config get MMCM_MAIN_OSC_SEL

```

A result of 0x1 indicates a system configured for TTC clock, while 0x0 indicates a local clock is in use. To change your clock selection run the following:

```

flx-config set MMCM_MAIN_LCLK_FORCE=0xN

```

For N = 0 or 1 as needed. It is also possible to select your clock source via the *elinkconfig* graphical tool. More information on this feature will be provided in Section 6.1.1.3.

Another way to view the overall clock status by running via the FELIX info tool, or flx-info. This can be run with no command line parameters to dump summary information for your board as follows:

#### flx-info

Clock settings can then be viewed in the 'Clock Resources' section, as shown in Figure 6.

#### Clock resources

-----

Local clock in use : YES Internal PLL Lock : YES

ADN2814 TTC Status: ON Figure 6. flx-info Clock Resources Output.

# 3.5.2. TTC Clock Recovery: ADN2814

Should you wish to use a TTC clock source, you must next check that your FELIX board's ADN2814 clock recovery chip[ADN2814] is functioning correctly. Non-TTC users can skip this section.

The overall status of your ADN2814 is reported in the Clock resources report from flx-info as show in Figure 6. For more detail on the chip's status, run with the following extra parameter:

#### flx-info ADN2814

If your chip is functioning correctly, and you have a TTC system connected, you should see output matching Figure 7.

TTC Status: ON

Loss of Signal Status: 0 Static Loss of Lock: 0 Loss of Lock Status: 0

Figure 7. flx-info ADN2814 status output.

If the output differs (e.g. if you see a loss of lock reported) please check your connections before resetting the ADN2814 using the following:

flx-reset ADN2814

# 3.5.3. Clock Jitter Cleaning

Whether you are using an internal or external clock, the signal must be cleaned to minimise jitter and ensure stable performance. FELIX uses one of two dedicated chips for jitter cleaning depending on your clock source and hardware.

TTC clocks should be cleaned by the *Si5345* chip[Si5345], which is hosted by the TTCfx v3 for VC-709 systems as well as on-board the BNL-711/712. Non-TTC clocks can also be cleaned by the Si5345, but for those who don't have a TTCfx v3 the VC-709 also hosts a different cleaning chip, the *Si5324*[Si5324], which offers sufficient jitter correction for the non-TTC case.

The Si5324 is currently only supported with a dedicated firmware build for those wishing to connect optical links to FELIX using the FULL mode protocol. Users of GBT must have a Si5345-based system. Should you wish to use the Si5324 please make sure to check the filename of the firmware tarball provided on the FELIX firmware distribution site to ensure the name of the cleaner is present.

Whichever your use case, your FELIX card must be configured to the correct jitter cleaner in order

to function correctly. This can be achieved using the flx-init command line application as follows

flx-init -T <N>

For Si5324 use N = 1, for Si5345 use N = 2.

you will have to redo this jitter cleaner initialisation step each time you change FELIX clock source to maintain normal operation.

To check the status of your jitter cleaner, use the following command:

flx-info <cleaner name>

# 3.6. Connecting and Initialising Optical Links

Assuming you have set up your FELIX clocks specified above for your use case, set up the FELIX software environment as described in Section 5 and programmed the FPGA aboard your VC-709 or BNL-711/712 as described in Section 4 you are now nearly ready to attempt to connect the system to a peer via optical link using either GBT or FULL mode protocols.

The first step to bringing up your links is to connect your fibres to the transceivers aboard the VC-709 or BNL-711/712, ensuring not to place excessive strain on them. Once the connectors are properly seated, you can check the physical status of your links.

## 3.6.1. Physical Link Layer Status: VC-709

In order to check the status of your physical connections for a VC-709 (which are SFP based) run the following:

flx-info SFP

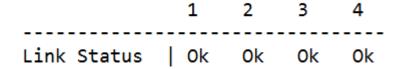

Look for the lines marked 'Link Status' in the output as per Figure 8

Figure 8. flx-info VC-709 SFP physical status output.

# 3.6.2. Physical Link Layer Status: BNL-711/712

In order to check the status of your physical connections for a BNL-711/712 (which are MiniPOD based) run the following:

flx-monitor POD

There will be many lines of output, but you should check the section labelled 'MiniPODs' as shown in Figure 9.

|                 | 1st 814      | 2nd 814   | 3rd 814 | 4th 814           | 1st 824 | 2nd 824 | 3rd 824 | 4th 824 |

|-----------------|--------------|-----------|---------|-------------------|---------|---------|---------|---------|

|                 |              |           |         |                   |         |         |         |         |

| Temperature [C] | 44.9         | 42.6      | 46.2    | 48.4              | 42.3    | 39.5    | 43.7    | 44.4    |

| 3.3 VCC [V]     | 3.28         | 3.25      | 3.27    | 3.26              | 3.28    | 3.29    | 3.28    | 3.28    |

| 2.5 VCC [V]     | 2.41         | 2.43      | 2.42    | 2.42              | 2.42    | 2.44    | 2.41    | 2.43    |

|                 |              |           |         |                   |         |         |         |         |

| LOS latched of  | channel:   ( | 0   1   2 | 3   4   | 5   6   7         | 8   9   | 10   11 |         |         |

|                 | ==           |           | -       |                   | -   :   |         |         |         |

|                 | 1st 814   I  | N   N   N | N   N   | N   N   N         | N   N   | N   N   |         |         |

|                 | 2nd 814   Y  | Y   Y   Y | Y   Y   | Y   Y   Y         | Y   Y   | Y   Y   |         |         |

|                 | 3rd 814   Y  | Y   Y   Y | Y   Y   | Y   Y   Y         | Y   Y   | Y   Y   |         |         |

|                 | 4th 814   Y  | Y   Y   Y | Y   Y   | Y   Y   Y         | Y   Y   | Y   Y   |         |         |

|                 | 1st 824   I  | N   Y   N | N   Y   | Y   Y   Y         | Y   Y   | Y   Y   |         |         |

|                 | 2nd 824   \  | Y   Y   Y | Y   Y   | Y   Y   Y         | Y   Y   | Y   Y   |         |         |

|                 | 3rd 824   \  | Y   Y   Y | Y   Y   | Y   Y   Y         | Y   Y   | Y   Y   |         |         |

|                 | 4th 824   \  | Y   Y   Y | Y   Y   | $Y \mid Y \mid Y$ | Y   Y   | Y   Y   |         |         |

|                 |              |           |         |                   |         |         |         |         |

Figure 9. flx-monitor BNL-711/712 MiniPOD physical status output.

If your physical link is working correctly you should see loss of latch status 'N' for the relevant MiniPOD, where 814 corresponds to Tx and 824 to Rx PODs respectively. For a physical map of MiniPOD locations please consult [app:bnl711] (same for both BNL-711 and BNL-712).

### 3.6.3. Logical Link Layer Initialisation

Once you have established a successful physical connection, the next step depends on your choice of logical protocol. If you are connecting with the FULL mode protocol your logical links should then come up immediately. You should therefore be ready to attempt to transfer data to FELIX.

If you are connecting with GBT you will need to train the links to bring them up by running the following:

#### flx-init

This should run reporting no errors. You can then print the status of your GBT links with:

#### flx-info GBT

The results should match Figure 10.

#### GBT CHANNEL ALIGNMENT STATUS

Figure 10. flx-info GBT status output (VC-709 version, a BNL-711/712 can have up to 24 channels displayed).

If this looks correct your GBT links should now be fully operational. Before attempting to transfer GBT data please ensure you have followed the guide in Section 6.1 for details on how to configure your E-links.

# Chapter 4. Firmware Releases and Programming

# 4.1. Firmware Distribution Protocol

#### 4.1.1. Release Announcements

FELIX firmware (and software) releases will be announced on the following e-group:

#### atlas-tdag-felix-users@cern.ch

Please subscribe to this group to stay up to date with the latest updates. All new releases will include a detailed change list and reference to the associated version of this user manual.

#### 4.1.2. Firmware Distribution Site

Tarballs of firmware releases (containing both .bit and .mcs files) are made available via a dedicate web page:

https://atlas-project-felix.web.cern.ch/atlas-project-felix/user/dist/firmware

Versioning information is available in the on-site 'bitfiles\_change\_log.md', please download the latest version as indicated.

all recent firmware revisions are labelled 'CLKSELECT' to indicate that they support both dual TTC and local clock sources. Older revisions were dedicated to one clock or another, but these should now be considered deprecated. Please upgrade to a newer revision if you have such a version.

# 4.1.3. Supported Link Protocols & Encoding

FELIX firmware builds currently support the following link protocols and encoding options as part of the standard release.

| Mode                   | Support |

|------------------------|---------|

| GBT Normal Mode 8b/10b | Y       |

| GBT Normal Mode HDLC   | Y       |

| GBT Normal Mode Direct | N       |

| GBT Wide Mode          | N       |

| FULL Mode              | Y       |

# 4.2. Firmware Programming

The FPGAs aboard both the VC-709 and BNL can be programmed directly via a JTAG interface using the Vivado™ software suite[vivado2016]. For the VC-709 this method also makes possible to

program the on-board FLASH ROM. A configuration programmed into the FPGA directly will be lost if the machine is switched off, whereas a configuration programmed in the FLASH will persist. This will make it possible to retain the desired programming state of the card e.g. if transported. This section will describe how to program the card using all available methods.

# 4.2.1. JTAG Connectivity

The VC-709 comes with an on-board JTAG programmer, accessible via USB, as described in Section 3. The BNL-711/712 does not have an on-board programmer, and as such you will need to acquire a USB-accessible programmer. The FELIX developers recommend the Digilent® HS2 for this purpose.

## 4.2.2. Setting up the Vivado™ Suite

Specific installation instructions for the Vivado™ suite are provided with your development kit. Note that the instructions in this section are compatible with the 2014, 2015 and 2016 releases of the suite. We recommend you install the software locally on the PC you wish to use as your programming server. This should be connected to your VC-709 in your FELIX host via USB as described in Section 3.2. When you first connect your system via USB you will need to run a Xilinx® setup script to configure the bus properly (path may vary depending on product year):

source Xilinx/Vivado/2016.4/data/xicom/cable\_drivers/lin64/digilent/install\_digilent.sh

The Vivado<sup>™</sup> environment can be started with the following commands:

source Xilinx/Vivado/2016.4/settings64.sh vivado &

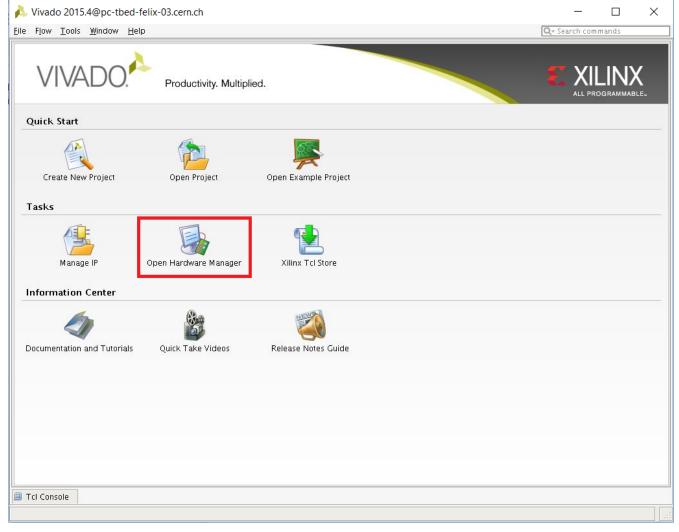

You will then be presented with the  $Vivado^{\infty}$  splash screen, where you should select 'Open Hardware Manager' as shown in the red box in Figure 11.

Figure 11. Vivado™ Splash Screen.

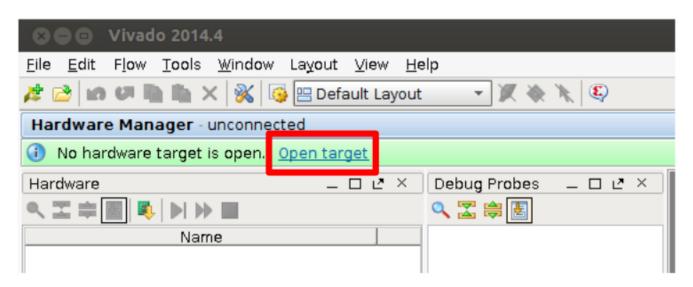

From the hardware manager select 'Open Target' on the top left as shown in Figure 12 and choose 'Open New Target'.

Figure 12. Vivado™ Hardware Manager.

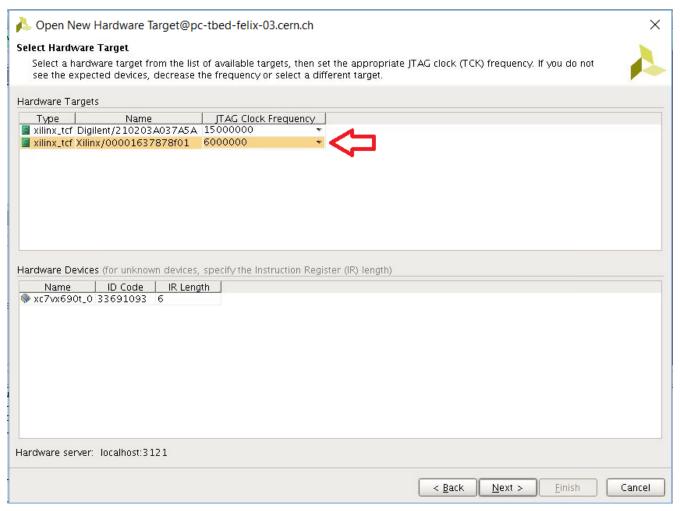

From this point, select 'Next' on the following screen and 'Connect to Local Server' after that, once again press 'Next'. This should bring you to the hardware list. On this screen select the FPGA on your VC-709 or BNL-711/712 from the uppermost list (if you have only one board there should be

only one entry, if not, find yours in the list by name). The screen you will see is shown in Figure 13. Once you have found your FPGA and selected it press 'Next' on the bottom right and 'Finish' on the following screen.

Figure 13. Vivado<sup>TM</sup> Target Selector with VC-709's Virtex7 FPGA selected, as indicated by red arrow (FPGA ID will vary from model to model). The BNL-711/712's Kintex Ultrascale FPGA will appear as  $x = 10^{-10}$

From here, you will be taken to the main programming interface, as shown in Figure 14. You are now ready to program your FPGA or FLASH.

Figure 14. Vivado™ Programming Interface.

## 4.2.3. Programming the FPGA Directly

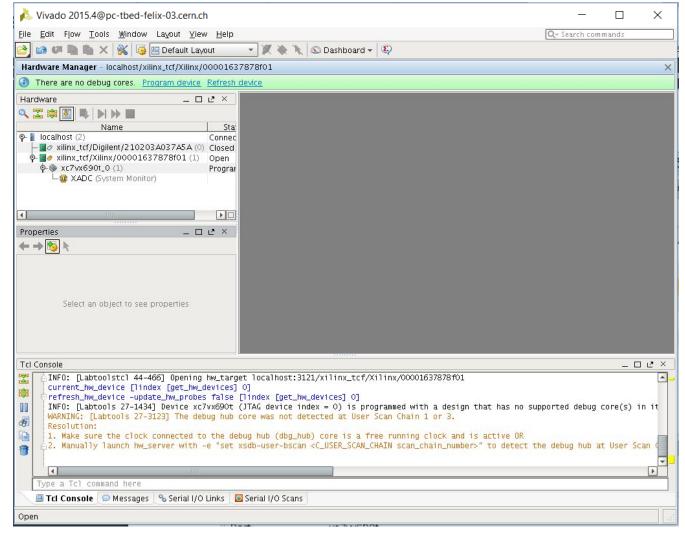

To program an FPGA directly, select it from the device list on the main programming window (as shown in Figure 15, right click and select 'Program Device'.

Figure 15. Selecting Device to Program.

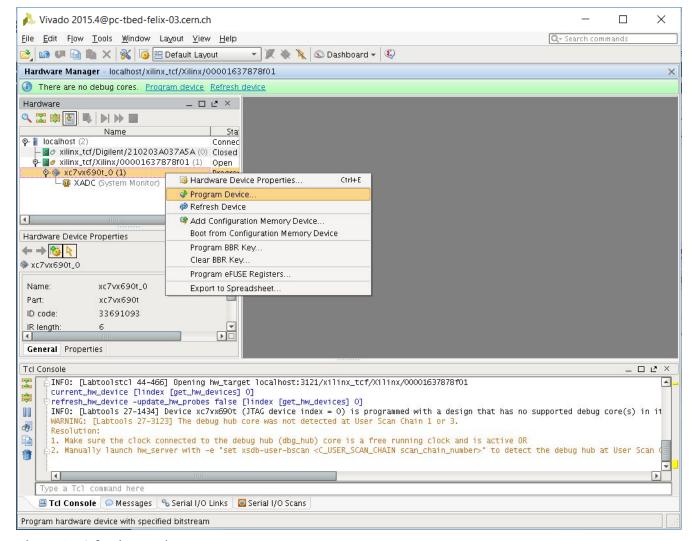

You will now be asked to select a .bit file as shown in Figure 16. This is available in the firmware release tarball as specified at the start of this chapter. You do not need to select a debug probes file. Once a file has been chosen, select 'Program' on the bottom right to write the file to the FPGA. Once complete your FPGA should now be fully reprogrammed.

Figure 16. Selecting Bit file to Program.

## 4.2.4. Programming the FLASH ROM (VC-709)

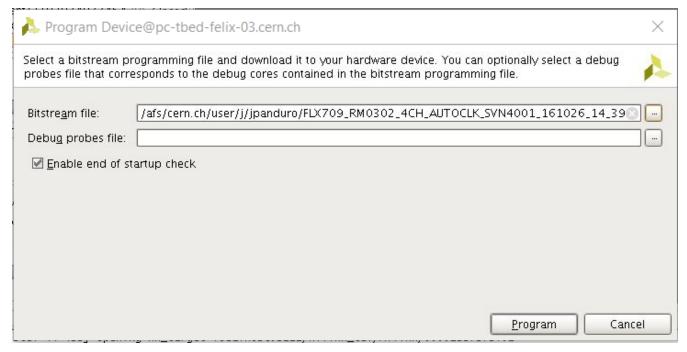

To program the FLASH ROM start once again from the main programming window. Find and right click on your FPGA and select 'Add Configuration Memory Device' in the list, as shown in Figure 17

Figure 17. Select Vivado™ Flash Programming Dialog.

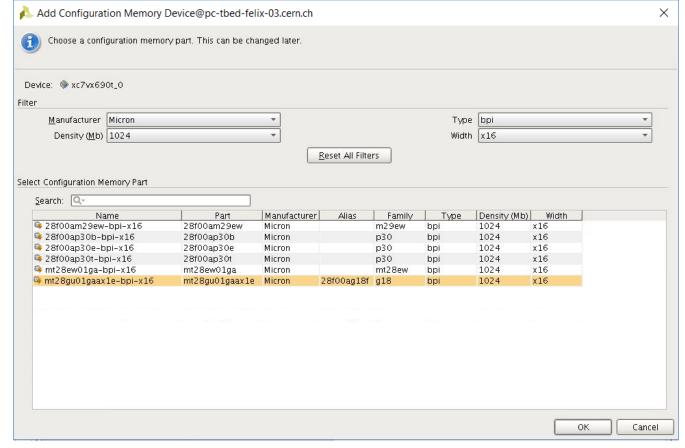

From here you will be taken to the a dialog requesting that you select the memory device you wish to program. On the VC-709 this will typically be a Micron memory device with given parameters. To find it quickly enter the criteria demonstrated in Figure 18 and select the device as shown. Look for the device with alias '28f00ag18f'.

Figure 18. Memory Device Selection Interface.

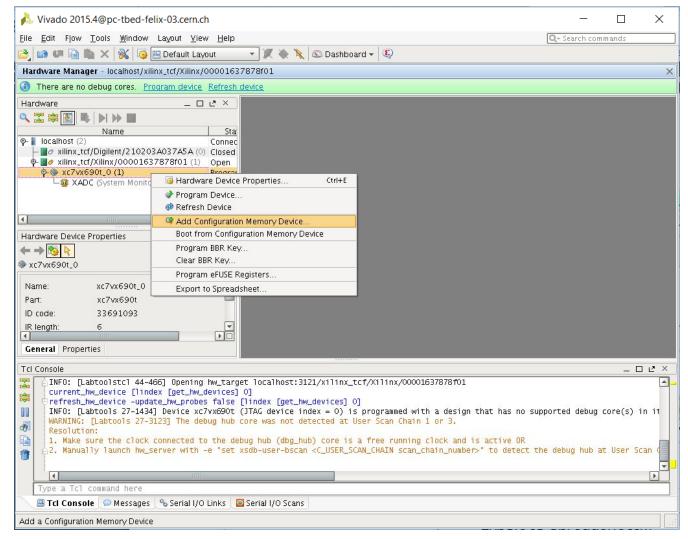

Once selected, press 'Ok' on the bottom right and 'Ok' again on the following window asking 'Do you want to program the configuration memory device now?'. On the subsequent dialog, choose the .mcs file you wish to program (provided with your firmware release) as shown in Figure 19. Select 'Ok' at the bottom to program the FLASH. Once complete your card should be programmed with a non-volatile firmware installation that will survive loss of power to the host.

| elect a configuration file and set pro | gramming options.                                                       |

|----------------------------------------|-------------------------------------------------------------------------|

| Memory Device:                         | mt28gu01gaax1e-bpi-x16                                                  |

| Configuration file:                    | 'user/j/jpanduro/FLX709_RM0302_4CH_AUTOCLK_SVN4001_161026_14_39.mcs 🕙 🕞 |

| PR <u>M</u> file:                      |                                                                         |

| State of non-config mem I/O pins:      | Pull-none 🔻                                                             |

| Program Operations                     |                                                                         |

| Address Range: Configura               | ation File Only                                                         |

| RS Pins: NONE                          | ▼                                                                       |

| <u> </u>                               |                                                                         |

| ☐ <u>B</u> lank Check                  |                                                                         |

| ✓ Program                              |                                                                         |

| ✓ Verify                               |                                                                         |

| ☐ Verify <u>C</u> hecksum              |                                                                         |

| SVF Options                            |                                                                         |

| ☐ Create <u>S</u> VF Only (no progran  | n operations)                                                           |

| SVF File:                              |                                                                         |

|                                        |                                                                         |

|                                        |                                                                         |

|                                        |                                                                         |

|                                        |                                                                         |

|                                        |                                                                         |

|                                        |                                                                         |

|                                        |                                                                         |

|                                        |                                                                         |

|                                        |                                                                         |

|                                        | OK Cancel Apply                                                         |

Figure 19. Selecting .mcs file to program.

## 4.2.5. Programming the FLASH ROM (BNL-711/712)

FLASH programming for the BNL-711/712 is done via means of the fflash application, which is provided as part of the FELIX software suite. Please consult the instructions provided in Section 6.5.7. Note that the BNL-711/712 has 4 different FLASH sectors which can be programmed. The board will by default come up from powercycle loaded from the sector specified by the jumper configuration described in [app:bnl711]. Please ensure you program the correct sector in order to see the expected image loaded.

# 4.2.6. Enabling new FPGA Configuration

If you have programmed our FPGA directly, please soft reboot your machine to pick up the new

configuration. For changes to the FLASH ROM a full powercycle may be needed to pick new firmware, unless you have manually programmed the FPGA from FLASH as described in Section 6.5.7. In the latter case a soft reboot will be sufficient.

#### PCIe hotplug procedure

Should you wish to avoid rebooting your machine (assuming a powercycle isn't required) it is possible to rescan the PCIe bus re-synchronise with the new firmware image. Note that this procedure hasn't been fully validated, and may produce inconsistent results. It should only be attempted if a reboot is prohibited. First, remove the device from the bus list as follows (root privileges needed):

```

echo 1 > /sys/bus/pci/devices/0000:<bus ID>/remove

```

(where you get the bus ID of the device from lspci)

Then, rescan the bus to bring the device back with:

```

echo 1 > /sys/bus/pci/rescan

```

It is also recommended that you restart the FELIX driver at this point to pick up the new image:

./etc/init.d/drivers\_flx restart.

# Chapter 5. Software Distribution and Installation

# 5.1. Software Distribution Protocol

## 5.1.1. Pre-requisites

FELIX software is now formally supported for systems using the SLC6 and CentOS operating systems.

#### 5.1.2. Release Announcements

FELIX software (and firmware) releases will be announced on the following e-group:

#### atlas-tdaq-felix-users@cern.ch

Please subscribe to this group to stay up to date with the latest updates. All new releases will include a detailed change list and reference to the associated version of this user manual.

#### 5.1.3. Release Distribution Site

The main distribution mechanism for new software releases is via a dedicated web page:

https://atlas-project-felix.web.cern.ch/atlas-project-felix/user/dist/software

Here users will be able to find the latest firmware and software. The newest recommended version is marked in all cases. Installation instructions for the software suite and driver can be found below.

#### **FELIX Driver**

The latest version of the FELIX driver is available on the distribution site within 'software/drivers'.

#### **FELIX Software Suite**

The latest version of the FELIX software suite is available on the distribution site in within 'software/apps'. The software release is provided as in tarball and rpm forms to suit different use cases. A docker image with the release pre-installed is also available.

# 5.2. Software Installation Instructions

#### 5.2.1. Driver RPM Installation Instructions

#### **DKMS**

The FELIX driver makes use of 'Dynamic Kernel Module Support' (DKMS) to automatically track kernel changes once installed. Users should therefore only need to change their installation if a new

version of the driver itself is released.

#### **Removal of Existing Driver Installations**

In order to update the FELIX driver it will first be necessary to remove any existing driver installations from your system. To do this please follow the procedure outlined below. You will require superuser privileges in order to perform the driver de-installation itself and subsequent cleanup.

To check if a driver is already installed issue the following command:

```

rpm -qa | grep tdaq

```

If a driver rpm is installed you'll see a response along the lines of:

```

tdaq_sw_for_Flx-4.0.3-2dkms.noarch

```

To remove the driver do the following (substituting 'filename' for the results of the search in the previous step):

```

rpm -e filename

```

Once this operation is complete you will be in a position to install the latest FELIX driver.

#### Installation of New Driver

To install the FELIX driver RPM, run the following command (superuser privileges required):

```

yum install tdaq_sw_for_Flx-4.0.3-2dkms.noarch.rpm

```

(this should take 1-2 minutes to complete, due to the need to compile the driver for your kernel as per the DKMS framework)

Once the driver is installed you should start it as follows (as superuser):

```

./etc/init.d/drivers_flx start

```

Once started you can check the status of the card using:

```

cat /proc/flx

```

You should see output along the lines of Figure 20 (will vary depending on your firmware version).

```

FLX driver for RM4.0 F/W and TDAQ for release tdaq710 for felix 4.0.3. Distributed with driver RPM 4.0.3

Debua

Number of cards detected

Locked resources

card | global_locks

0 | 0x00000000

Locked resources

card | resource bit | PID | tag

=====|======|=====|=====|=====

--- cype : 709

Device type : 0x7038

FPGA_DNA : 0x71e1085c

Reg Map Version : 4 4

Build revision 'G

Card 0:

Build revision (GIT version): rm-4.4

Date and time : 30-10-2018 at 20h50 GIT commit number : 116

: 0xe91d2276

GIT hash

: GBT

Firmware mode

Firmware mode : GBT

Number of descriptors : 2, Number of interrupts

Number of descriptors

: 2, Number of interrupts

: 8

Interrupt count |

0 |

0 |

0 |

0 |

0 |

0 |

Interrupt flag |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

Interrupt mask |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

MSIX PBA 00000000

The command 'echo <action> > /proc/flx', executed as root,

allows you to interact with the driver. Possible actions are:

-> Enable debugging

nodebug -> Disable debugging

eloa

-> Log errors to /var/log/message

noelog

-> Do not log errors to /var/log/message

-> Enable compatibility with RM3 F/W

rm4

-> Disable compatibility with RM3 F/W

swap -> Enable automatic swapping of 0x7038 / 0x7039 and 0x427 / 0x428 noswap -> Disable automatic swapping of 0x7038 / 0x7039 and 0x427 / 0x428

clearlock -> Clear all lock bits (Attention: Close processes that hold lock bits before you do this)

```

Figure 20. Example output from /proc/flx

#### **Driver Flags**

The /proc/flx interface makes it possible to toggle certain parameters by issuing the following command:

```

echo <action> > /proc/flx

```

By substituting <action> it is possible to do the following (only a selected list below):

- Enable/disable compatibility mode with RM3 with the parameter 'rm3' or 'rm4' respectively.

- Enable/disable automatic re-ordering of FELIX cards to a more intuitive order w.r.t device type ('swap' or 'noswap').

- Clear all device locks with 'clearlocks'

## 5.2.2. Installation of FELIX Software Suite

The FELIX software release is available pre-compiled as a tarball which can be installed anywhere and then set up for use by running a command line script. Each user can download their own version, or the release can be installed centrally and the location of the script shared with users.

To unpack the tarball, run the following command:

#### tar -xvzf <filename>

Once unpacked, a setup script must be run to enable access to all libraries and binary files. The script can be run as follows from the release base directory:

## source felix-04-00-03/x86\_64-slc6-gcc62-opt/setup.sh

This script will need to be run with every new session, or added to the environment setup procedure. Once complete you should have access to all FELIX software. In the next section we will describe how to test your installation to verify full functionality.

# Chapter 6. Basic Tools

The FELIX software suite comprises both high and low level tools. At the highest level, the FelixCore application is responsible for communication and bulk dataflow in a full slice system. At a lower level, the suite provides a number of tools, both command line and GUI based, to facilitate system configuration and testing. This chapter will describe these low level tools such that users will be able to effectively communicate with, configure and test their system.

If you are looking to set up a full system slice with data output to a network please consult Section 7, which describes the FelixCore Application and NetIO library. This section assumes that you have set up your FELIX software environment as described in Section 5. None of the tools in this section should require superuser privileges to run. All tools presented below work in both GBT and FULL mode, and for VC-709 and BNL-711/712, unless otherwise stated. Where special parameters are needed to distinguish modes this will be indicated.

A quick reference for all tools to be covered in this section is presented in Table 1.

the FELIX software suite contains a number of tools which are considered for developer use only. All tools which are rated for use by front-end users are listed in this document. Use of any other software is not recommended unless asked to do so by a FELIX developer.

Table 1. List of all recommended user tools. For more information on each please click the tool name to visit the dedicated section of this document.

| Low L               | evel Tools                                                                                |  |  |  |

|---------------------|-------------------------------------------------------------------------------------------|--|--|--|

| flx-<br>info        | View FELIX hardware and firmware status information                                       |  |  |  |

| flx-<br>confi<br>g  | View and modify low-level firmware parameters                                             |  |  |  |

| flx-<br>init        | Initialise FELIX, as well set as low level GBT and clock/jitter cleaning parameters       |  |  |  |

| flx-<br>reset       | Reset FELIX or specific component                                                         |  |  |  |

| flx-<br>monit<br>or | Status information for FPGA, LTC2991[ltc2991] or Minipod devices on a BNL-712 or BNL-712. |  |  |  |

| Dataf               | Dataflow Tools                                                                            |  |  |  |

| fdaq                | Receive data from FELIX and save to files or perform sanity checks                        |  |  |  |

| fuplo<br>ad         | Upload data through FELIX to a front-end E-link                                           |  |  |  |

| FELIX               | FELIX Configuration Tools                                                                 |  |  |  |

| Low L               | evel Tools                                                                                      |  |  |  |

|---------------------|-------------------------------------------------------------------------------------------------|--|--|--|

| elink<br>confi<br>g | GUI for link and data generator configuration.                                                  |  |  |  |

| felink              | Calculate link IDs given inputs with differing formats.                                         |  |  |  |

| ferev<br>erse       | Reverse the endianness of data passing through an E-link.                                       |  |  |  |

| fgpol<br>arity      | Switch 0/1 polarity of all data coming or going through a specific GBT link (formerly fgpolar). |  |  |  |

| fecon<br>f          | Upload link and/or data generator configuration to FELIX from the command line.                 |  |  |  |

| femu                | Control FELIX data generators.                                                                  |  |  |  |

| feto                | Control FELIX timeouts (global, TTC and link data, a.k.a 'instant timeout').                    |  |  |  |

| fflash              | Command line programming tool for firmware images in BNL-711 or BNL-712.                        |  |  |  |

| Gener               | al Debugging Tools                                                                              |  |  |  |

| fchec<br>k          | Perform configurable sanity checks on data from a file or dump selected data blocks to screen.  |  |  |  |

| fedu<br>mp          | Perform sanity checks on data from a file or dump selected data blocks from a file to screen.   |  |  |  |

| fec                 | Demo control and communication with GBT-SCA chip (GPIO, ADC, DAC and I2C).                      |  |  |  |

| Remo                | Remote Communication and Configuration Tools.                                                   |  |  |  |

| fic(e)              | Read or write GBTx chip registers via the GBT-link.                                             |  |  |  |

| fgbtx<br>conf       | Read or write GBTX registers via a GBT-SCA I2C channel. (formerly fgconf).                      |  |  |  |

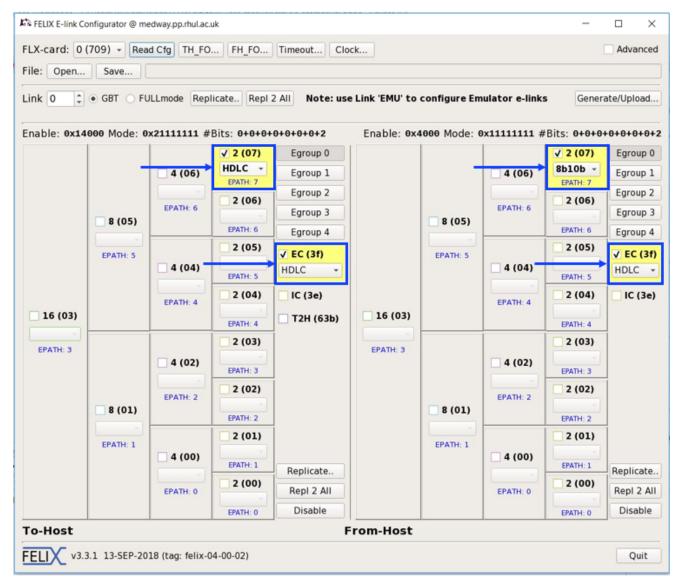

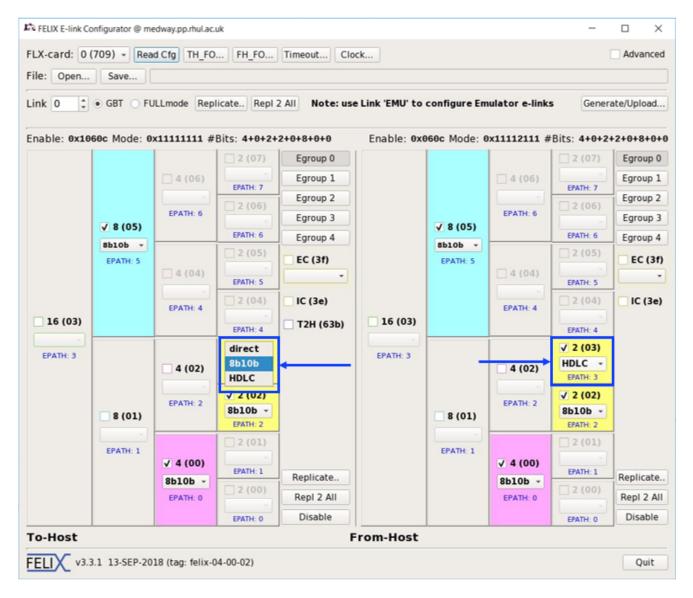

# 6.1. E-link Configuration with elinkconfig

Before FELIX can be used to transfer data its input and output links must be configured. The link configuration for a given FELIX card can be accessed and modified using the 'E-link configurator' application, or 'elinkconfig'. This is a GUI based tool to compile an E-link configuration or to inspect and/or edit the E-link configuration read from a given card, and to write the configuration and corresponding emulator data contents to a given card. The tool supports both GBT and FULL mode.

the link configuration must be manually refreshed every time a FELIX FPGA is reprogrammed, including power-cycling of a host!

To run the elinkconfig application issue the following command:

#### elinkconfig

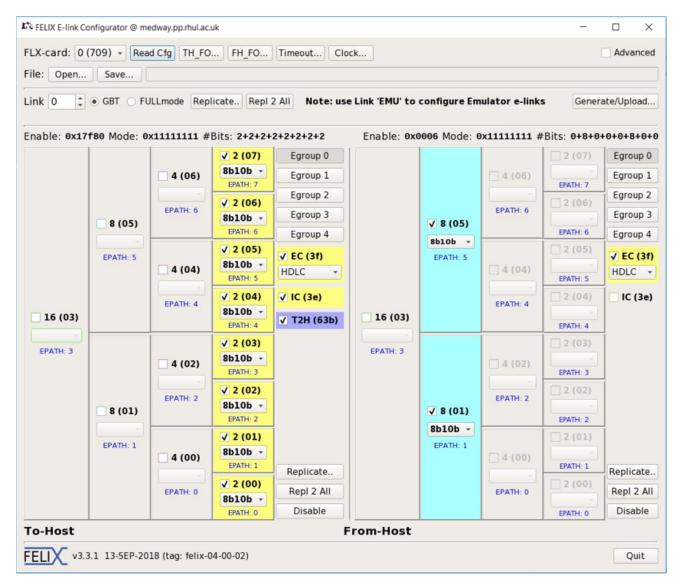

From here you will reach the main configuration panel as shown in Figure 21

Figure 21. Main panel - elinkconfig

The elinkconfig interface is split into three main areas. At the top there are two control bars to set FELIX card parameters, open/save configuration files as well as link selectors. The left main panel displays the from front-end to FELIX/host configuration for the selected link.

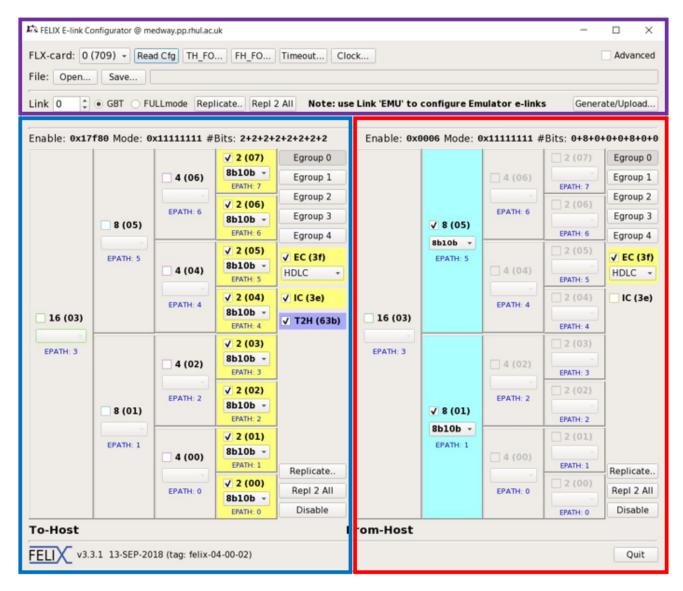

Figure 22. elinkconfig panel split. The uppermost panel (purple box) controls global settings and GBT selection. The left main panel contains the E-link configuration for the from front-end to host direction, the left main panel the from host to front-end direction

#### 6.1.1. Global Panel

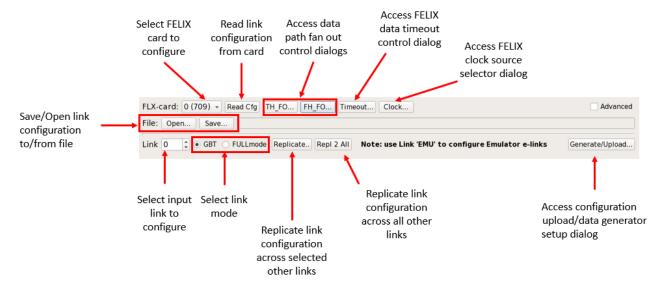

The elinkconfig global panel, shown in more detail in Figure 23 provides the top level interface for the tool. From there it is possible to select which FELIX card within your system you wish to configure, which link within that card, which link mode, as well as a number of other configuration properties. It is also possible to open previous configuration files, save new ones, and read the current configuration from the selected FELIX card.

This panel also contains an advanced developer feature allowing you to select the maximum chunk size for a given E-link width - users are recommended to avoid changing these settings as they may cause unexpected behaviour.

Figure 23. elinkconfig global panel.

From the global panel it is possible to access a number of sub-panels, as indicated in Figure 23. These give access to more advanced configuration options, details of which are presented below.

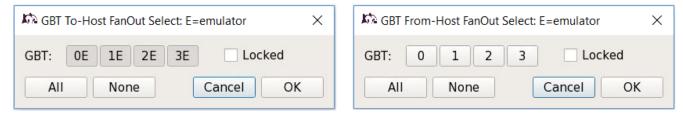

#### Data Path Fan Out Selectors: TH\_FO and FH\_FO

FELIX operates two separate data generators within its firmware, one attached directly to the data path going to the host, and one attached to the path going towards the front-end. While the generators are attached, they have mutually exclusive access to the data path with regular non-emulated data in both directions. To avoid the two data types colliding only one type may access the path at a time. The fan out selectors control this access by ensuring that only internally emulated data or external data can be configured to pass at any one time. Most FELIX applications are able to configure these selectors automatically, but for the purposes of user testing it may be necessary to set these values manually. The selectors are accessed via the TH\_FO (to host) and FH\_FO (from host) buttons in the global panel. The resulting dialogs are presented in Figure 22.

Figure 24. Fan out control for to-host (left) and from-host (right) directions. The setting for each link is displayed separately (in this case for a 4-link VC-709 system). It is also possible to lock the settings using the dedicated checkbox.

In order to switch the selector value simply open the required dialog and click on the link number you wish to toggle. A link displayed with its number alone is set to external data, if a link is displayed with its number plus 'E' it is in emulation mode. It is also possible to set/unset all values using the 'All' and 'None' buttons provided.

Changes made in this dialog are immediately propagated to the FELIX card in question once you select 'OK'.

In some cases a user may wish to prevent other applications from automatically changing these

settings. For example, if a specific link is nominated for TTC information transfer it may be convenient to fix this to external data for the duration of a test. In this case it is possible to lock the values by selecting the 'locked' check box. Applications will then be unable to change these settings until the card is reconfigured from this interface or the FPGA is reprogrammed. More information on configuring TTC transfer to the front-end are available in Section 6.1.3 below.

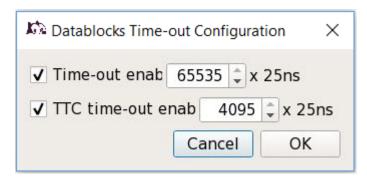

#### **Data Timeout Control Dialog**

FELIX offers the facility to time out pending incoming data after a configurable window from receipt of the first related packets. This is applicable for both regular and TTC data (in the to-host direction). Should data time out then all available blocks are transferred to the host. The timeout feature is enabled by default, but can me modified or disabled/re-enabled via the control dialog accessible by selecting the 'Timeout' button in the global panel. This will open the dialog shown in Figure 25. From here it is possible to disable/enable both regular data and TTC timeouts using the check boxes, as well as modify the timeout window sizes. This should typically only be done under the guidance of a FELIX developer for debugging purposes.

Changes made in this dialog are immediately propagated to the FELIX card in question once you select 'OK'.

Figure 25. elinkconfig data timeout control dialog.

EC and TTC2Host data are always subjected to an immediate time-out, independent of the global time-out. In addition it is possible to enable a time-out per E-link independent of the global time-out setting, which may be important for E-links carrying irregular and small data fragments such as those connected to GBT-SCA devices.

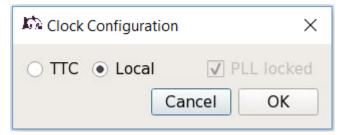

#### **Clock Source Selector Dialog**

As mentioned in Section 3.5.1, FELIX supports two different firmware clock sources. It is possible to switch between these sources from elinkconfig from the clock source selector dialog, accessible by clicking the 'clock' button in the global panel. The selector dialog is shown in Figure 26, and is a simple two button toggle between TTC and local clock.

Changes made here will be immediately propagated to the FELIX card in question once you select 'OK'.

Please also consult Section 3.5.3 before making any clock changes, to ensure you correctly configure your FELIX card's jitter cleaner post-clock change to ensure continued stable operation.

Figure 26. elinkconfig clock source selector dialog.

#### 6.1.2. To-Host Panel

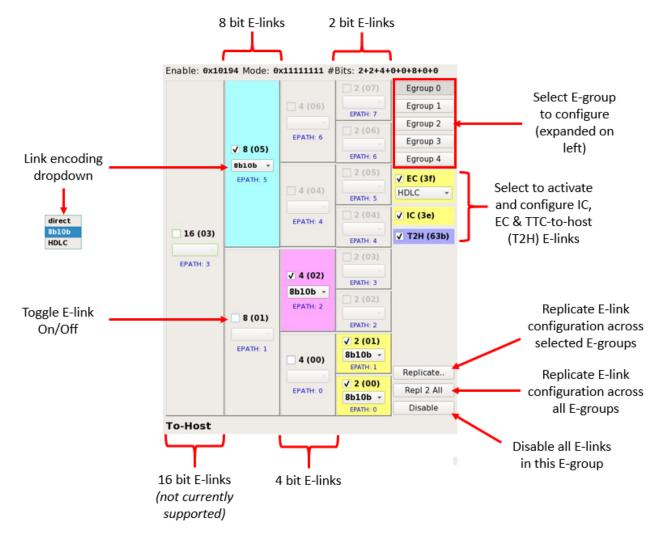

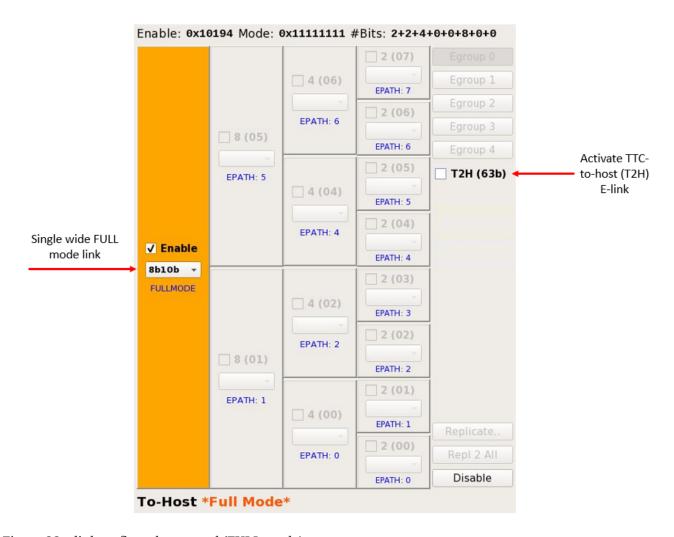

The to-host panel provides access to the configuration of the currently selected link (GBT or FULL mode) in the to-host direction. The type of panel to show can be selected in the global panel as described in Figure 23. In the GBT case it is possible to configure the complete set of E-links associated with this link, split up by E-group. It is also possible to configure the SCA and TTC links (see Section 6.1.6.4 for more info), the latter of which provides L1 accept information to the host. For each link it is also possible to select the type of encoding to be used, although 8b10b is recommended for all regular data links. A more detailed look at this panel is presented in Figure 27.

Figure 27. elinkconfig to-host panel (GBT mode). Various configuration options and tools are indicated as they appear in the panel. Note, on a GBTX it is not possible to have different-width E-links within one E-group (even if elinkconfig permits it).

In FULL mode this panel provides fewer options, as such this link mode does not contain logical E-

link subdivisions. This version of the panel is presented in Figure 28.

Figure 28. elinkconfig to-host panel (FULL mode).

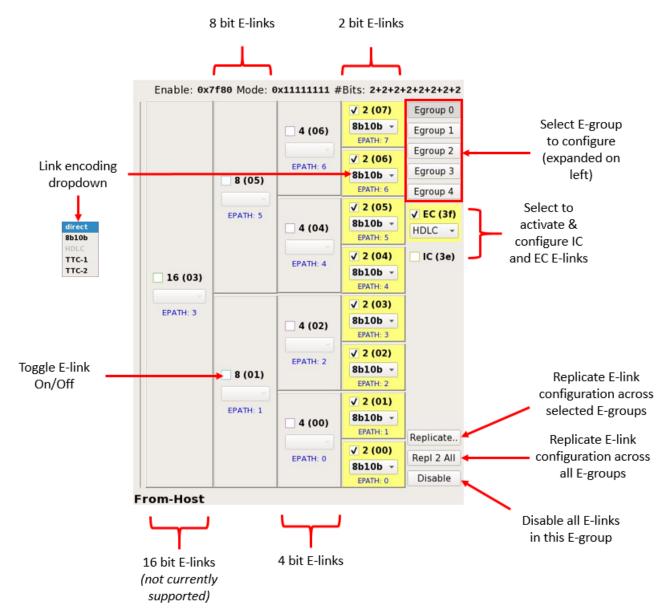

#### 6.1.3. From-Host Panel

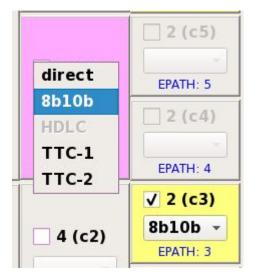

The from-host panel makes it possible to configure the GBT links transporting data from FELIX towards connected front-end electronics. This panel only exists in GBT mode form as FULL mode is only a to-host protocol, and any FULL mode firmware will implement from-host links as GBT. A more detailed look at this panel is presented in Figure 29. A key difference between this panel and the to-host panel is that the link encoding available also includes several different TTC paths (in this case TTC-1 and TTC-2 are shown) which are for the propagation of TTC information from FELIX to the front-end. Depending on the E-link width used TTC paths from 0 to 4 are can be made available. Using this encoding selector it is therefore possible to nominate specific E-links to carry TTC data as needed.

Figure 29. elinkconfig from-host panel (GBT mode). Various configuration options and tools are indicated as they appear in the panel.

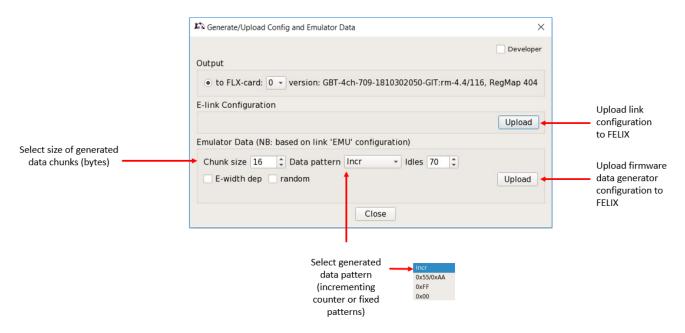

## 6.1.4. Link and Data Generator Configuration Upload Dialog

The to-and-from host panels allow you to put together a complete configuration set for all links handled by a given FELIX card. Once you have prepared your desired configuration, you can upload it to the FELIX in question by selecting the 'Generate/Upload' button in the upper panel on the right. This will open the upload dialog, as shown in Figure 30. The GBT version is shown, but the FULL mode variant is essentially identical, beyond some disabled developer features.

The E-link mapping for the FELIX data generators can be configured by selecting the 'EMU' link in elinkconfig (in previous versions this was done by selecting any GBT link). If the option to save to a file is used the emulator config is now saved separately to the rest of the links. If an older configuration file (which does not contain the new emulator configuration data) is read into the tool and uploaded, the configuration of link 0 is automatically used in its place.

Once the panel is prepared, select 'Upload' from the middle box labeled 'E-link Configuration' to write your configuration to the card. If you also wish to configure the FELIX on-board data generators for tests in emulation mode select the 'Upload' button in the lower 'Emulator Data' box.

If you are running in emulation mode and wish to change your E-link configuration you must remember to upload to the emulator every time you upload a change.

In FULL mode the data generators will only produce FULL mode data in the to-host direction. In the to-front-end direction GBT data will be produced. In GBT mode GBT data will be produced in both directions.

Figure 30. elinkconfig upload panel. Any features not indicated with arrows should be considered for experts only, and used only under consultation with a FELIX developer.

Once your configuration is uploaded you can then proceed to use the FELIX system as normal, the new settings will take effect immediately. To avoid unexpected behaviour please avoid reconfiguring the links while the FELIX card in question is in active use in your system.

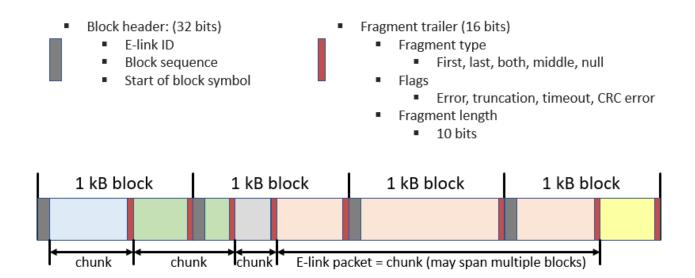

## 6.1.5. Guide to Valid E-link Configurations

The E-link configuration uploaded to a FELIX card is actually a set of instructions to a component known as the *Central Router*. This is responsible for sending incoming data (in either direction) to the correct remote end point, as defined by E-link. For FULL mode there is no such thing as an E-link, and so the Central Router merely propagates a wide stream of bits across the link. In the GBT case, E-links are defined as separate logical links within a given physical GBT link. E-links can have (in the current implementation) three different bit widths, which given the link clock defines the maximum bandwidth they can sustain. The widths are 2, 4 and 8 bits, running at 40, 80 and 160 MHz respectively. There is currently no support for 16 bit E-links. A GBT link can therefore be considered as a logical aggregation of low bandwidth links into one high bandwidth transfer. For full details please consult the official documentationSection 8.1.2.2.

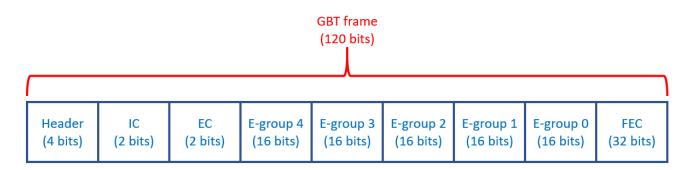

In 'Normal' mode, a GBT link is 80 bits wide, and this puts an upper limit on the number of E-links. It is therefore possible to have few wide 8 bit links, a larger number of narrower 2 or 4 bit links, or a mixture of the two. Should a GBT be operated in 'Wide' mode (not currently supported) then a further 32 bits are available within the GBT link (i.e. 112 in total), allowing for more E-links. The

structure of a normal mode GBT frame is shown in Figure 31. It is up to the user to decide how much of the GBT width to utilise as per their front-end needs. It is permitted to leave link bandwidth unused by not assigned E-links to that part of the GBT frame.

elinkconfig allows it, but on a GBTX it is not possible to have different-width E-links within one E-group.

Figure 31. Bit structure of a GBT frame, showing E-groups, IC and EC links, as well as GBT header and Forward Error Correction (FEC).

Within a given GBT link, logical links are subdivided for management purposes into 16 bit wide 'Egroups'. Each E-group logically contains a combination of E-links up to an aggregate of 16 bits of width, looking at either extreme this means up to 8 of the narrowest 2 bit E-links at one end, or two of the widest 8 bit E-links at the other. The E-group is the unit of connectivity around which the elinkconfig interface is built, with the to and from-host panels designed around E-group granularity.

Looking within the E-group, there is one further layer of link identification to consider. Each group supports up to 8 logical 'E-paths'. These correspond to the logical connection end-points which the Central Router supports. For each E-group it is therefore only possible to send data to 8 destinations, which is designed to correspond to the maximum number of 2 bit E-links. However, the E-path structure imposes an additional restriction on E-link assignment. Because of the routing structure the E-path end points needed by E-links of different widths can overlap, meaning only a link of one width or the other is possible. Consider the routing diagram presented in the to-host panel in Figure 27. This display is designed to mirror the structure of the Central Router to make the dependencies as transparent as possible to users.

The active 4 bit E-link in this panel is using E-path 2. This means not only that E-path 2 is unavailable for the 2 bit E-link which could be assigned to that path (see the column to the right) but also the 2 bit E-link for E-path 3, as the wider 4 bit link in E-path 2 overlaps with it. It is therefore possible to either have the 4 bit E-link active, or one or both of the 2 bit links, but 4 bit link cannot be active at the same time as either 2 bit link. Note that this doesn't affect the E-link which could be active in E-path 1, as this doesn't overlap. In this case this link is disabled through user choice, not through any logical limitation. However, if you wanted to enable the 8 bit wide E-link at E-path 1, this would overlap with all 2 and 4 bit E-links to its right, meaning only it could be active.

To summarise, in order to build a valid link configuration no two links using the same E-path can be active at the same time within an E-group. Depending on the width of the link in question this may also disqualify other links of smaller width if they overlap with it. For this reason, elinkconfig

will not allow you to select overlapping links.

Within a given link map, each E-link can be configured to use different encoding formats as per front-end requirements. This area is still subject to active development, and it is strongly recommended that users work towards basing systems on 8b10b encoding. For FULL mode 8b10b is also the default.

There is a known issue with GBTx chips whereby links disconnected from any front-end source generate spurious data at random intervals. If using FELIX with a GBTx it is strongly recommended that any links which are disconnected from the front-end be deactivated in elinkconfig. This will prevent spurious data causing confusion in front-end testing.

#### **Semi-Static Firmware E-link Configuration**

In the 24-channel GBT mode build, the FELIX firmware does not support fully configurable E-links due to the need to conserve FPGA resources. The set of configurable E-links in this case is described below.

|           | From Host                | To Host    | Encoding   |

|-----------|--------------------------|------------|------------|

| EC link   | SCA                      | SCA        | 2 bit HDLC |

| E-Group 0 | 8 x SCA                  | 8 x SCA    | 2 bit HDLC |

| E-Group 1 | 2 x 8 bits or 8 x 2 bits | 8 x 2 bits | 8b/10b     |

| E-Group 2 | 2 x 8 bits or 8 x 2 bits | 4 x 4 bits | 8b/10b     |

| E-Group 3 | 2 x 8 bits or 8 x 2 bits | 4 x 4 bits | 8b/10b     |

| E-Group 4 | 2 x 8 bits               | 4 x 4 bits | 8b/10b     |

### 6.1.6. Guide to common configuration tasks

#### Working with E-link configurations stored in files

elinkconfig can read and store configuration sets in .elc files. In order to load a previously existing configuration set into the tool simply select 'Open' from the global panel and choose the file to be loaded. The GUI will be automatically updated to reflect the new configuration. From here you can modify the configuration (if needed) by e.g. using the to and from-host panels to enable/disable E-links. Once your changes are complete you can upload the new configuration to the FELIX card of your choice using the 'Generate/Upload' button in the global panel. Make sure to upload both the link and data generator configurations if you wish to use the latter. Finally, you can save your modified configuration to a file by selecting 'Save' from the global panel.

#### Modifying the existing E-link configuration on a FELIX card without a file

If you are working without .elc files and wish you modify the existing configuration on a card you must first load it into the tool by selecting the card in question via the global panel and then pressing the 'Read Cfg' button. This will populate the GUI with the configuration currently active on the card. From here you can modify the configuration as required and upload a new version to the card as advised above. You can also save your configuration to a file.

#### **Configure L1AInfo E-links to host**

The FELIX firmware implements a dedicated 'virtual' E-link for this purpose of transferring Level-1 Accept information to the host system for transfer to subscribers on the network. Each FELIX card provides one such E-link, which may be activated by ticking the checkbox on the right hand side of the To-Host panel in elinkconfig, as shown in Figure 27. The E-link ID on which the data will be transferred is shown in the tool.

Each such E-link will provide a 20-byte 'L1AInfo' block containing information for each Level-1 Accept. The contents of the block are presented in Figure 32. More details on this and other FELIX data structures is available in [app:datastructures].

| 0 | FMT(8)    | Len(8) = 20 | reserved     | BCID(12) |  |

|---|-----------|-------------|--------------|----------|--|

| 1 | XL1ID(8)  | L1ID(24)    |              |          |  |

| 2 | orbit(32) |             |              |          |  |

| 3 | Trigger   | Type (16)   | reserved(16) |          |  |

| 4 | L0ID(32)  |             |              |          |  |

L1Ainfo\_v01

Figure 32. The Level-1 Accept information message sent to the Back end software (20 bytes) as seen as five 32-bit word.

#### **Configure TTC E-links from host**

Users may configure any number of to-front-end links for the purpose of transferring TTC information to their electronics. The TTC data arriving at the FELIX card will be automatically decoded, and subsets made available to users for relay to front-ends in a configurable manner. The subsets which can be sent depend on the width of the E-link chosen for the transfer.

The current configuration sets are presented in Table 2, although this can evolve based on user requirements. For example, 2-bit E-links can only be configured in 'TTC-0' mode, meaning only the L1A and the full, non-decoded B-channel data stream can be sent. Alternatively, 4-bit E-links can be configured to send L1Accepts, Bunch Counter and Event Counter Resets, and a choice of either the non-decoded B-channel data stream or a user defined broadcast bit. Detector groups should communicate to the FELIX group which bits in which locations they need.

Table 2. Possible TTC options (Brcst[7:2] are the TTC user defined broadcast command bits (Brcst[1] is ECR, Brcst[0] is BCR). Bit 0 is the first bit transmitted out.

| E-link option | bit 7 | bit 6 | bit 5 | bit 4 | bit 3   | bit 2 | bit 1  | bit 0 |

|---------------|-------|-------|-------|-------|---------|-------|--------|-------|

| 0: 2<br>bits  |       |       |       |       |         |       | B-chan | L1A   |

| 1: 4<br>bits  |       |       |       |       | B-chan  | ECR   | BCR    | L1A   |

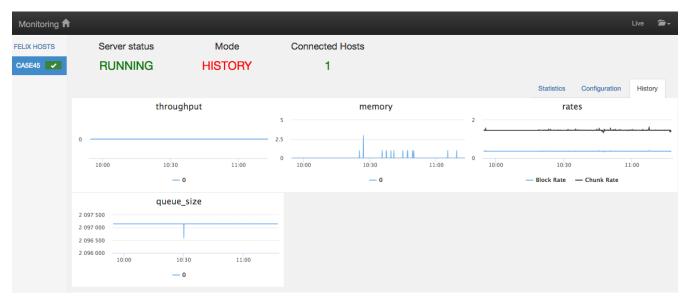

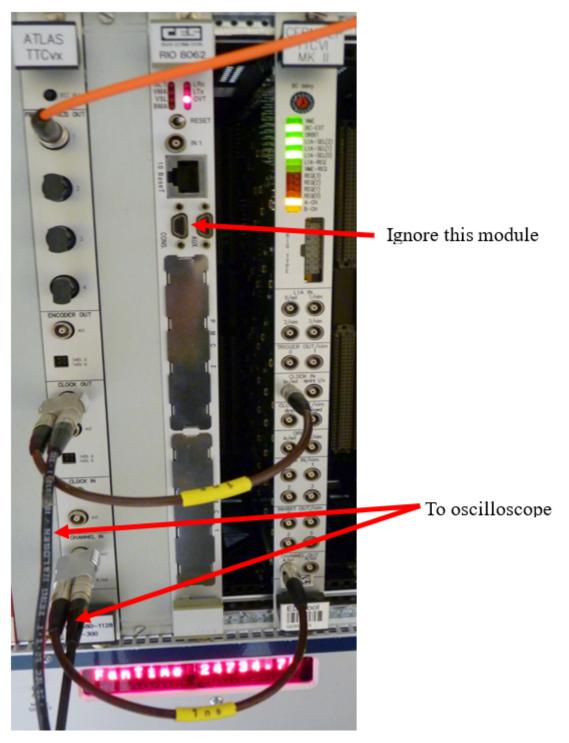

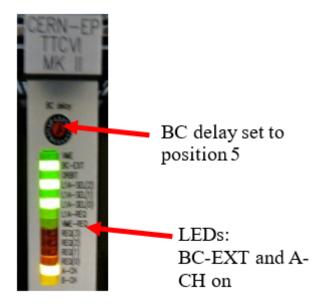

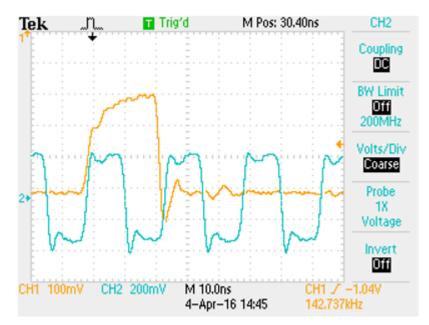

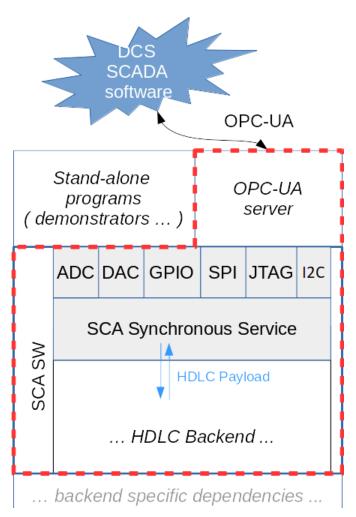

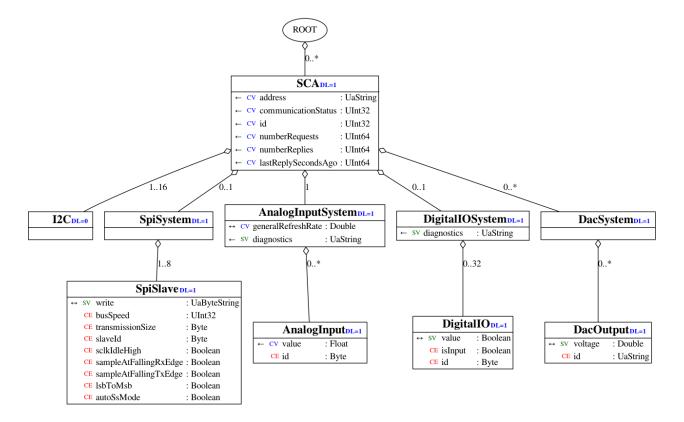

| 2: 4<br>bits  |       |       |       |       | Brcst[2 | ECR   | BCR    | L1A   |