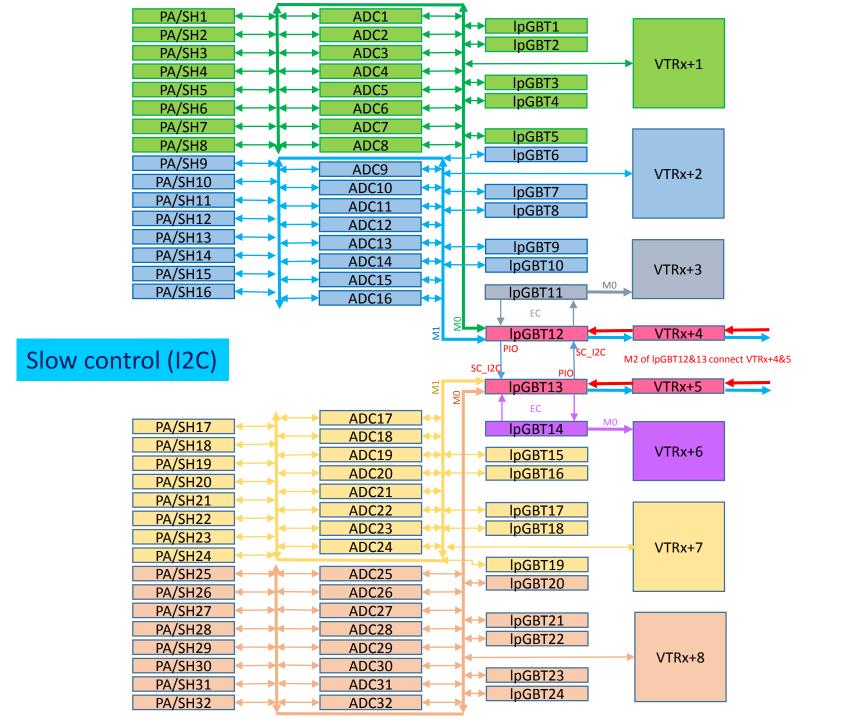

# FEB2 block diagrams

J. Bán, G. Brooijmans, J. Parsons, W. Sippach Nevis Laboratories

2.56GHz

10.24GHz

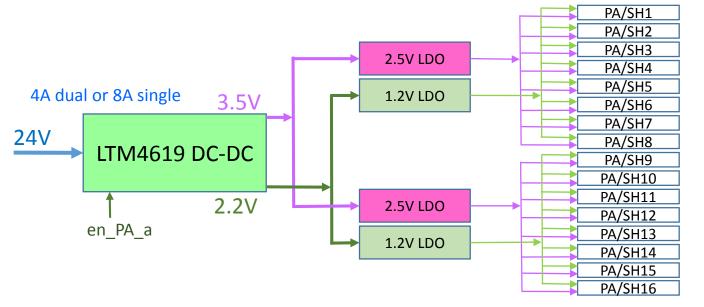

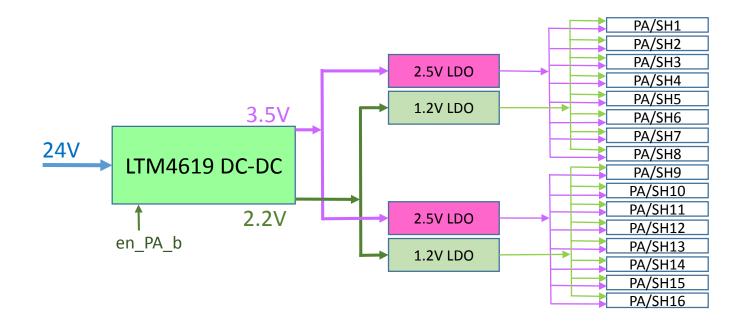

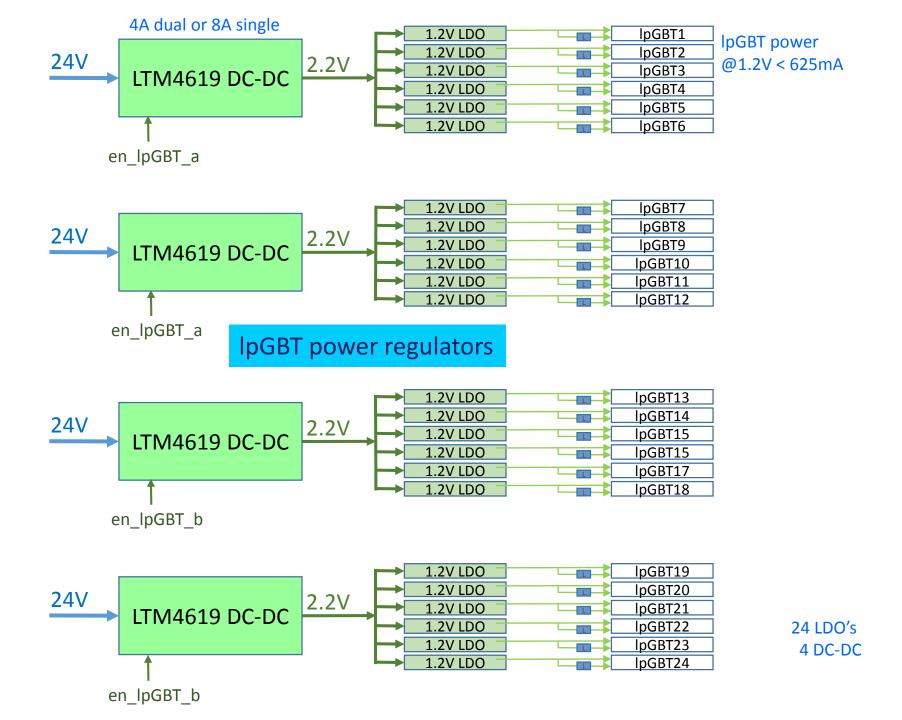

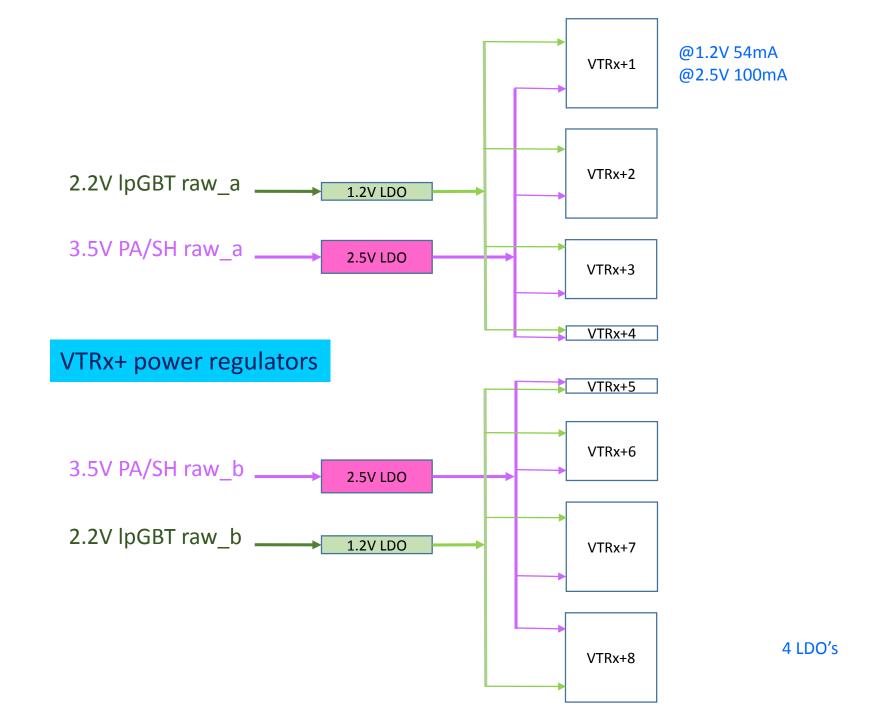

#### PA power @2.5V < 100mA @1.2V < 100mA

#### PA/SH power regulators

8 LDO's 2 DC-DC

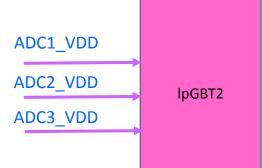

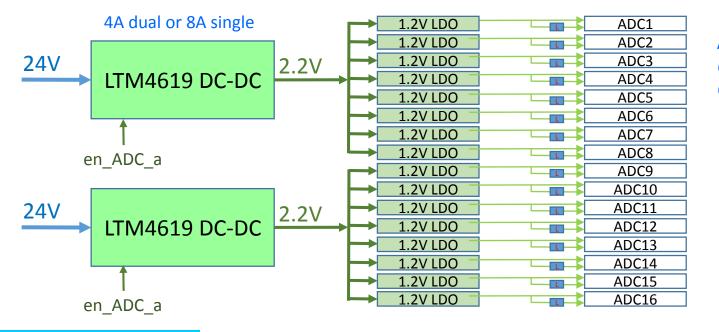

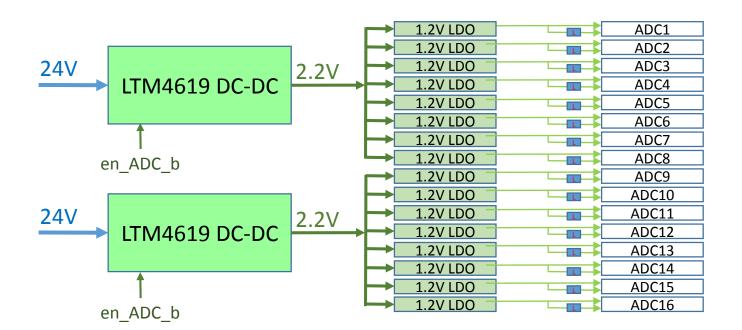

ADC power @1.2VA < 610mA @1.2VD < 70mA

#### ADC power regulators

32 LDO's 4 DC-DC

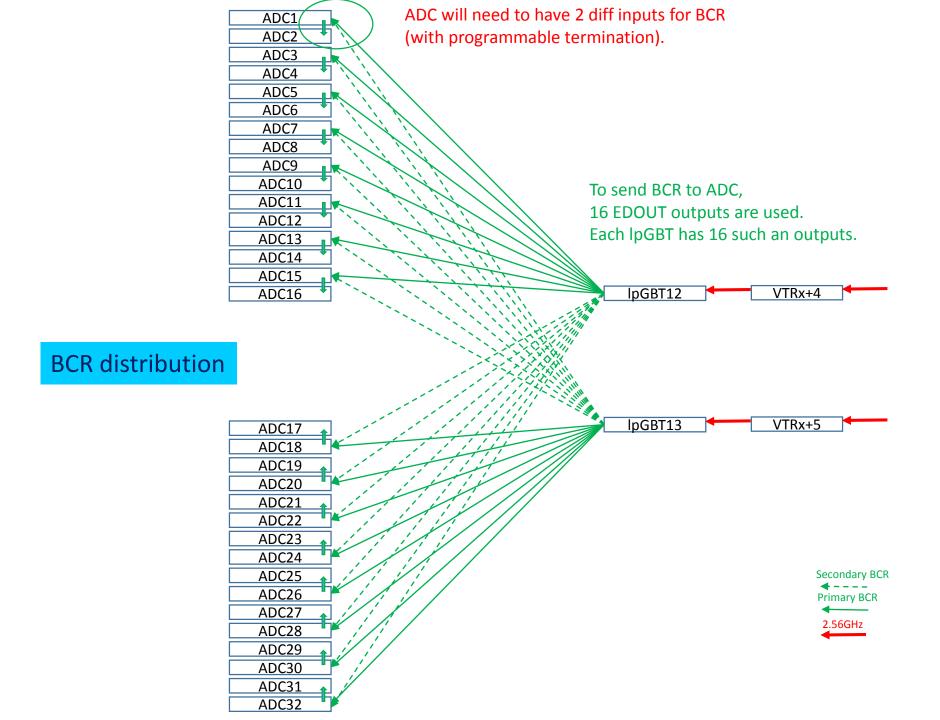

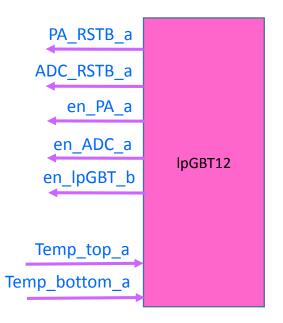

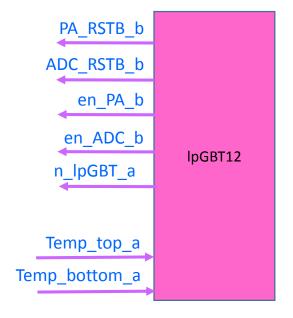

To generate resets and enable DC-DC conveters, PIO pins are used.

Each lpGBT has 16 such an outputs.

To measure the board temperatures, Internal ADC is used. Each IpGBT has 7way MUX to ADC.

### Slow control & monitoring (1)

## Slow control & monitoring (2)

To measure the regulator voltages, an internal IpGBT ADC is used. Each IpGBT has 7way MUX to ADC.

Typical PS output measurement scheme. All PA and ADC power supply voltages are going to measured.